# **Esses winbond sesses**

# **W681307 Product Datasheet**

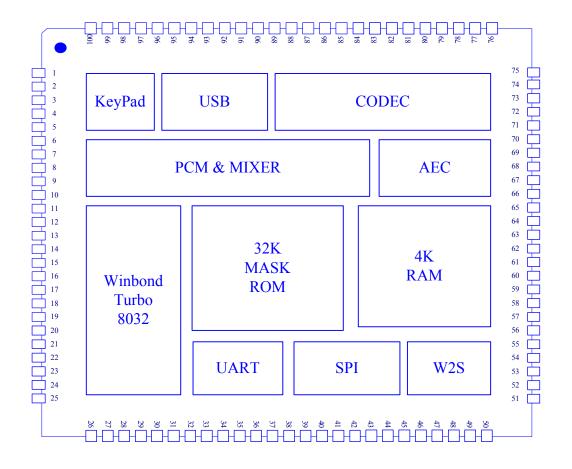

USB1.1 CODEC Microprocessor

Control Unit with 32KB Mask ROM

and 4KB RAM.

#### AMENDMENT HISTORY

| Ver | Date       | Filename                | Author | Changes (•: modified, √: added, x: removed)                           | Reference                  |

|-----|------------|-------------------------|--------|-----------------------------------------------------------------------|----------------------------|

| 1.0 | 2006/11/22 | W681307_Data Sheet_V1.0 | MCSu   |                                                                       |                            |

| 1.1 | 2006/12/02 | W681307_Data Sheet_V1.1 |        | <ul><li>Modify register 0x14C4.</li><li>Modify Figure 14-2.</li></ul> | W681307_Data<br>Sheet_V1.0 |

| 1.2 | 2006/12/28 | W681307_Data Sheet_V1.2 | MCSu   | • Modify register 0x14E5.                                             | W681307_Data<br>Sheet_V1.1 |

| 1.3 | 2007/07/23 | W681307_Data Sheet_V1.3 | TYChiu | • Modify endpoint table 18.2.1.                                       | W681307_Data<br>Sheet_V1.2 |

# **Esses winbond sesses**

**CONTENTS**

| 1.     | GENERAL DESCRIPTION                                                       | 9    |

|--------|---------------------------------------------------------------------------|------|

| 2.     | FEATURES                                                                  | - 10 |

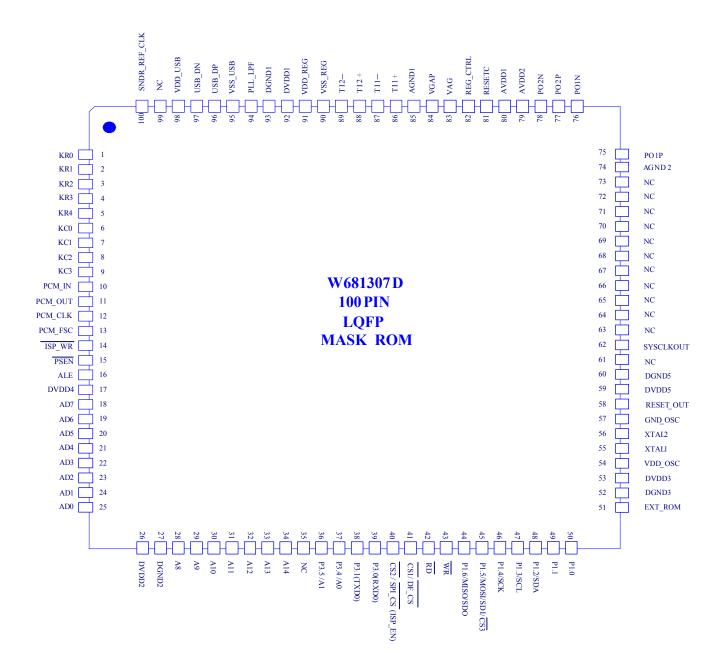

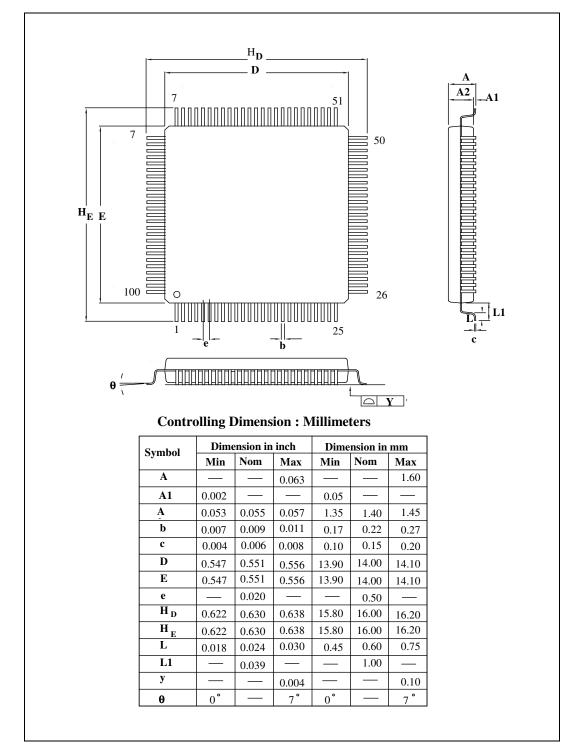

| 3.     | PIN CONFIGURATION                                                         | - 11 |

| 4.     | PINS DESCRIPTION                                                          | - 12 |

| 5.     | SYSTEM DIAGRAM                                                            | - 17 |

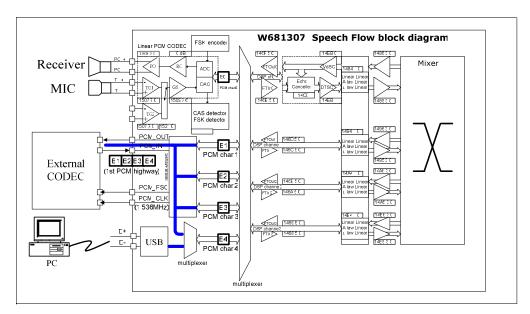

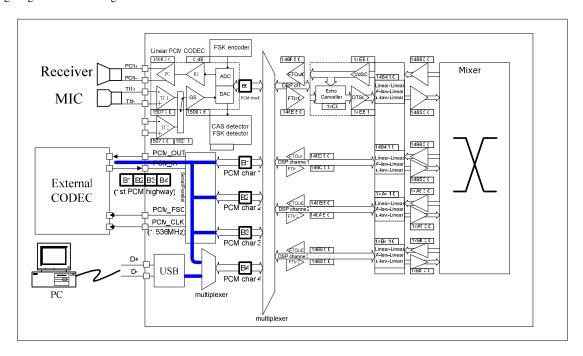

| 5.1    | Function Block Diagram                                                    | - 17 |

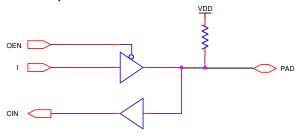

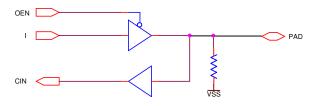

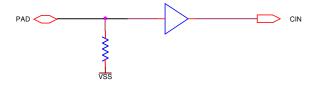

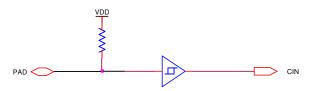

| 5.2    | I/O Cells in Winbond MCU Chip                                             | - 18 |

| 6.     | ELECTRICAL CHARACTERISTICS                                                | - 20 |

| 6.1    | Absolute Maximum Ratings                                                  | - 20 |

| 6.2    | DC Characteristics                                                        | - 20 |

| 6.3    | Analog Transmission Characteristics                                       | - 21 |

| 6.3.1  | Amplitude Response for Analog Transmission Performance                    | - 21 |

| 6.3.2  | Distortion Characteristics for Analog Transmission Performance            | - 21 |

| 6.4    | Analog Electrical Characteristics                                         |      |

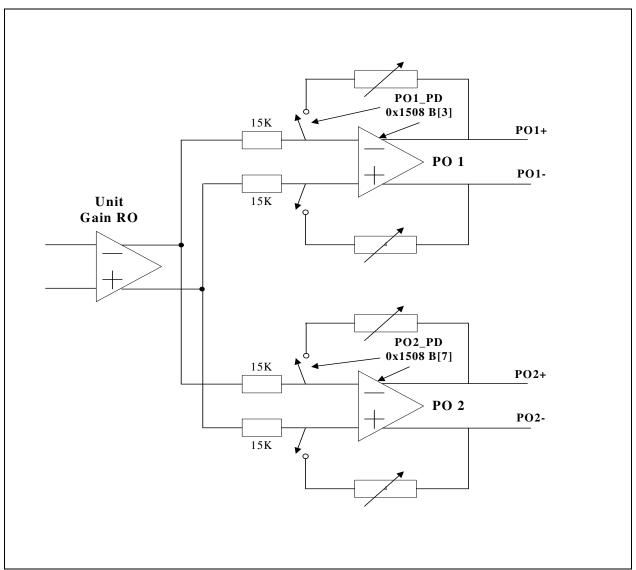

| 6.5    | Power Drivers – PO1, 2                                                    | - 22 |

| 6.6    | Programmable Output Linear Regulator                                      |      |

| 6.7    | USB PHY Electronic Characteristics (25°C, VDD_USB = 3.3V, DVDD1, 3 =1.9V) | - 23 |

| 6.8    | USB PLL Electronic Characteristics ( 25°C, AVDD = 3.3V, DVDD1, 3 =1.9V)   | - 24 |

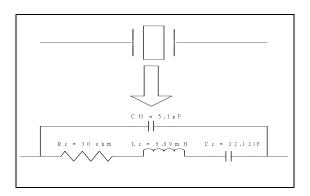

| 6.9    | The Crystal Specification Requirement                                     | - 24 |

| 6.10   | Recommended Crystal Specification                                         |      |

| 7.     | MEMORY AND REGISTER MAP                                                   |      |

| 7.1    | Program Memory Map                                                        |      |

| 7.2    | Data Memory Map                                                           |      |

| 7.3    | Register Map                                                              |      |

| 7.3.1  | Mixer and Speech Logic Registers Overview                                 |      |

| 7.3.2  | Support Logic Registers Overview                                          |      |

| 7.3.3  | Interface Logic Registers Overview                                        |      |

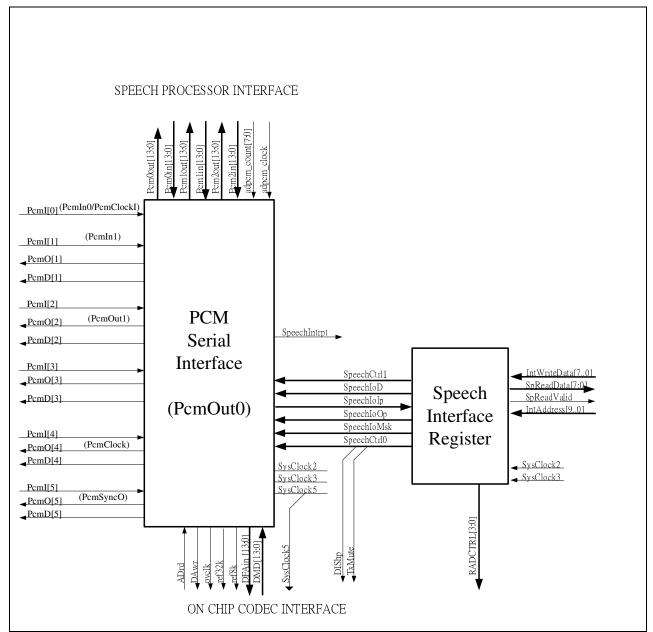

| 7.3.4  | Speech Interface Registers Overview                                       |      |

| 7.3.5  | Processor Interface Registers Overview                                    |      |

| 7.3.6  | Transcoder DSP Registers Overview                                         |      |

| 7.3.7  | Echo Canceller Registers Overview                                         |      |

| 7.3.8  | Soft Clip Registers Overview                                              |      |

| 7.3.9  | CODEC Digital Part                                                        |      |

| 7.3.10 |                                                                           |      |

| 7.3.11 | 1                                                                         |      |

| 7.3.12 |                                                                           |      |

| 7.3.13 |                                                                           |      |

| 7.3.14 | O                                                                         |      |

| 7.3.15 |                                                                           |      |

| 7.3.16 | 00 0 0                                                                    |      |

| 7.3.17 |                                                                           |      |

| 7.3.18 | 0                                                                         |      |

| 7.3.19 |                                                                           |      |

| 7.3.20 | ,                                                                         |      |

| 7.3.21 |                                                                           |      |

| 7.3.22 | O .                                                                       |      |

| 7.3.23 | B Data Flash SPI Interface Registers Overview                             | - 36 |

# massa winbond sassa

| 7.3.24 | W2S Interface Registers Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - 36 - |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 7.3.25 | USB Control Registers Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - 37 - |

| 7.3.26 | S ISP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 38 - |

| 8.     | SUPPORT LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 39 - |

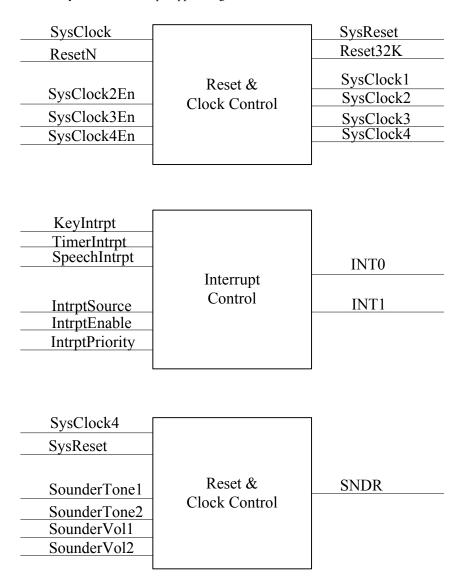

| 8.1    | Clock Control & Reset 32K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - 40 - |

| 8.1.1  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 40 - |

| 8.1.2  | Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 40 - |

| 8.1.3  | Clock Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 40 - |

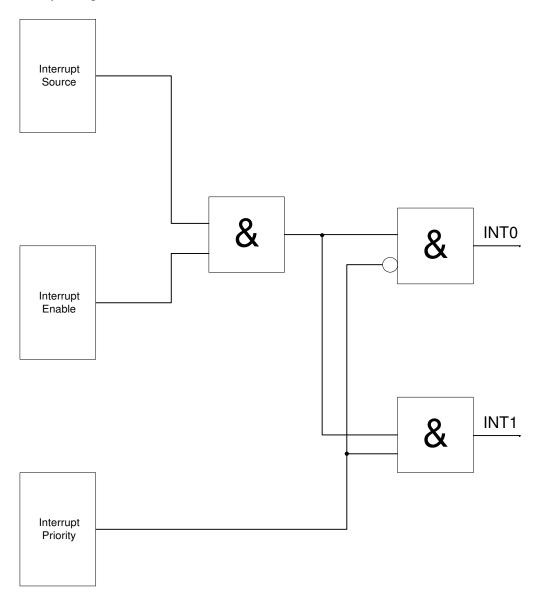

| 8.2    | Interrupt Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - 41 - |

| 8.2.1  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 41 - |

| 8.2.2  | Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 41 - |

| 8.2.3  | Interrupt Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 43 - |

| 8.2.4  | Extends of interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | - 44 - |

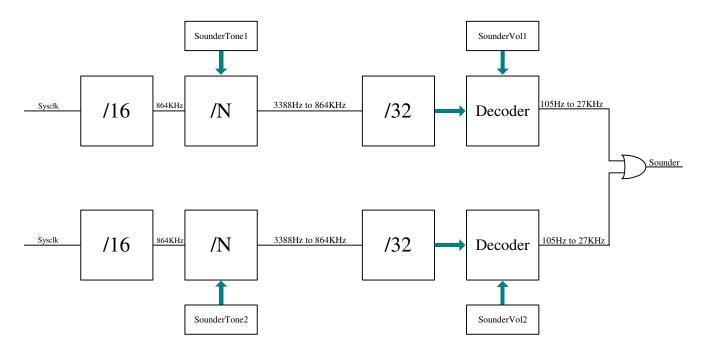

| 8.3    | Ringer Tone Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 45 - |

| 8.3.1  | Överview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | - 45 - |

| 8.3.2  | Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | - 45 - |

| 8.3.3  | Sounder Tone Register Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 8.3.4  | Sounder Volume Register Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| 8.3.5  | Example of use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| 8.3.6  | Sounder Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

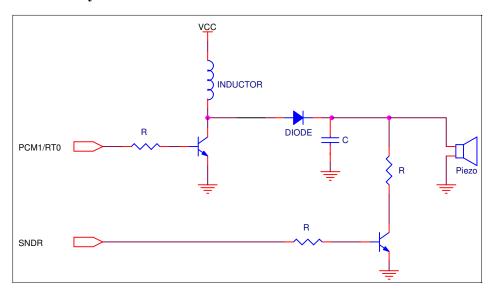

| 8.4    | PIEZO Tone Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

| 8.4.1  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 8.4.2  | Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| 9.     | INTERFACE LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

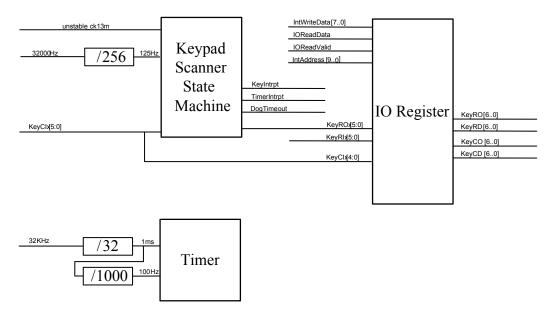

| 9.1    | Keypad Scanner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| 9.1.1  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 9.1.2  | Use of the Keypad Scanner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| 9.1.3  | Use of a Software Keypad Scanner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

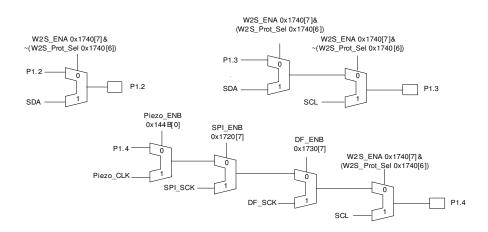

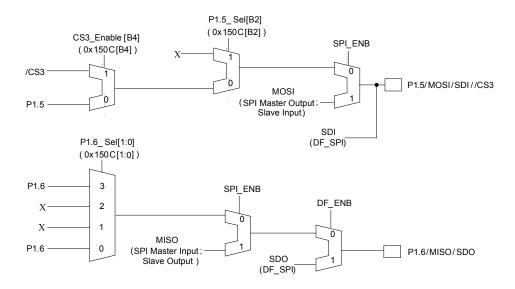

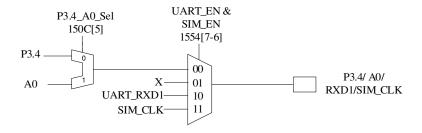

| 9.2    | I/O Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |

| 9.3    | Keypad Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| 9.3.1  | Key Location and Size Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

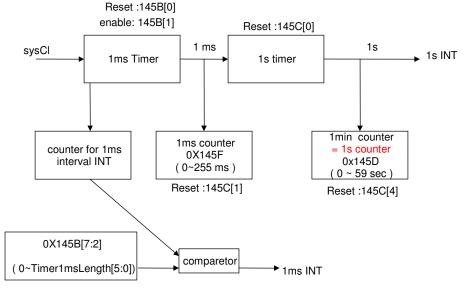

| 9.4    | Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| 9.4.1  | Watch Dog Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| 9.4.2  | Timer 1ms Control1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |