Silicon Radar GmbH Im Technologiepark 1 15236 Frankfurt (Oder) Germany

fon +49 335 / 228 80 30 fax +49 335 / 557 10 50 info@siliconradar.com www.siliconradar.com

# LNA\_024\_005

Low Noise Amplifier 24 – 29 GHz

# **Preliminary Data Sheet**

|           | •                  |                                   |                            |         |

|-----------|--------------------|-----------------------------------|----------------------------|---------|

| Status:   | Date:              | Author:                           | Filename:                  |         |

| Final     | 05-Nov-2021        | Silicon Radar GmbH                | Datasheet_LNA_024_005_V1.0 |         |

| Version:  | Product number:    | Package:                          | Marking:                   | Page:   |

| 1.0       | LNA_024_005        | QFN16, 3 × 3 mm <sup>2</sup>      | LNA005<br>YYWW             | 1 of 14 |

| Document: | Annex to VA_U03_01 | Anlage 8_Template_Datenblatt_RevE | Date: 19-May-2020          | Rev E   |

### **Version Control**

| Version | Changed section          | Description of change                        | Reason for change                  |

|---------|--------------------------|----------------------------------------------|------------------------------------|

| 0.1     | All                      | Document creation                            |                                    |

| 0.2     | 4.1 Absolute Max Ratings | ESD robustness values defined                | ESD test passed                    |

| 1.0     | Raised to final version  |                                              | According to QMS release procedure |

|         | Figure 14 added          | Reference planes for S-parameter measurement | Clarification                      |

## **Table of Contents**

| 1   | Features                      | 4  |

|-----|-------------------------------|----|

| 1.1 | Overview                      |    |

| 1.2 | Applications                  |    |

| 2   | Block Diagram                 |    |

| 3   | Pin Configuration             |    |

| 3.1 | Pin Assignment                |    |

| 3.2 | Pin Description               |    |

| 4   | Specification                 | 6  |

| 4.1 | Absolute Maximum Ratings      |    |

| 4.2 | Operating Range               | 7  |

| 4.3 | Thermal Resistance            |    |

| 4.4 | Electrical Characteristics    | 7  |

| 5   | Packaging                     | 8  |

| 5.1 | Outline Dimensions            | 8  |

| 5.2 | Package Footprint             | 8  |

| 5.3 | Package Code                  | 9  |

| 5.4 | Qualification Test            | 9  |

| 6   | Application                   | 9  |

| 6.1 | Application Circuit Schematic | 9  |

| 6.2 | Evaluation Board              | 10 |

| 6.3 | Input / Output Stages         | 10 |

| 7   | Measurement Results           | 11 |

|     |                               |    |

### 1 Features

- Low-noise amplifier (LNA) for 24-GHz ISM band an beyond

- Single supply voltage of 3.3 V

- Low power consumption of 18 mW

- Fully ESD protected device

- Gain control input

- Power-down mode

- Fast on / off switching for pulsed operation

- QFN16 leadless plastic package 3 mm × 3 mm

- Pb-free, RoHS compliant package

- IC is available as bare die as well

#### 1.1 Overview

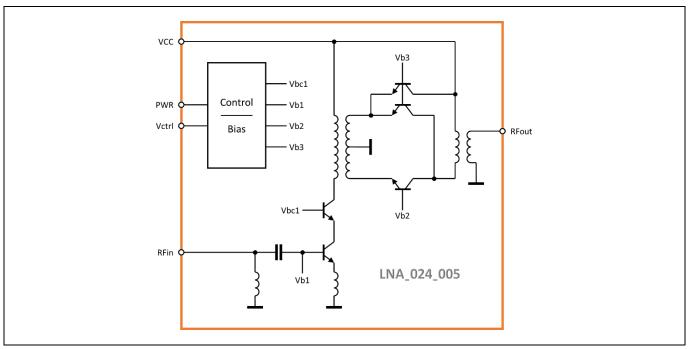

The low-noise amplifier LNA\_024\_005 is a two stage amplifier operating in two gain modes (high gain and low gain) with a power-down feature. The first stage employs a cascode configuration with inductive load and inductive emitter degeneration for stability reasons. The input matching network of the LNA consists of shunt inductor and series capacitor. The input shunt inductor provides ESD protection. In order to provide compact design and galvanic isolation between amplifier stages, transformers were used for interstage coupling and output matching. The second stage is a common-base structure with two gain states. This stage is loaded with a transformer providing appropriate output impedance. The gain mode is defined by an external digital signal at the Vctrl input. The LNA can be powered down via the PWR pin.

The LNA\_024\_005 features improved ESD robustness and replaces its predecessor LNA\_024\_004.

#### 1.2 Applications

The main use of the LNA is in wireless communication systems and in radar systems for the ISM band at 24 GHz and for ultra-wide band systems up to 29 GHz.

## 2 Block Diagram

Figure 1 Block Diagram

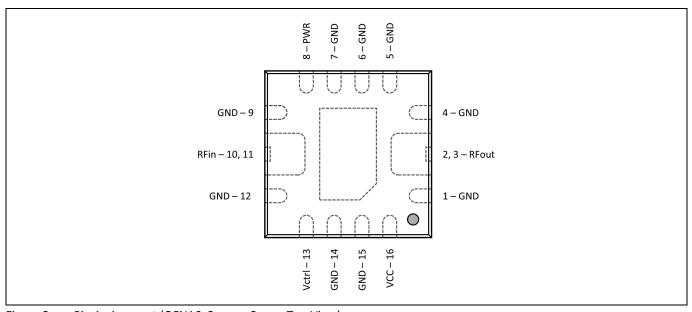

## **3** Pin Configuration

#### 3.1 Pin Assignment

Figure 2 Pin Assignment (QFN16, 3 mm × 3 mm, Top View)

#### 3.2 <u>Pin Description</u>

Table 1 Pin Description

| Pin  |       | Description                                                                                                                                       |  |  |  |  |  |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| No.  | Name  |                                                                                                                                                   |  |  |  |  |  |

| 1    | GND   | Ground                                                                                                                                            |  |  |  |  |  |

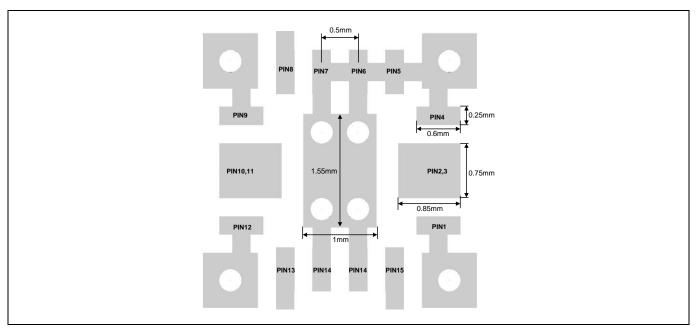

| 2    | RFout | RF output, $50 \Omega$ . Pin 2 and 3 have to be shorted on board close to the QFN package.                                                        |  |  |  |  |  |

| 3    | RFout | (See recommended land pattern in Figure 4.)                                                                                                       |  |  |  |  |  |

| 4    | GND   |                                                                                                                                                   |  |  |  |  |  |

| 5    | GND   | Ground                                                                                                                                            |  |  |  |  |  |

| 6    | GND   | Ground                                                                                                                                            |  |  |  |  |  |

| 7    | GND   |                                                                                                                                                   |  |  |  |  |  |

| 8    | PWR   | Power-down input: high – power-down, low – operate. PMOS input with pull-down resistor as shown in Figure 9, Equivalent I/O Circuits.             |  |  |  |  |  |

| 9    | GND   | Ground                                                                                                                                            |  |  |  |  |  |

| 10   | RFin  | RF input, $50\Omega$ . Pin 10 and 11 have to be shorted on board close to the QFN package.                                                        |  |  |  |  |  |

| 11   | RFin  | (See recommended land pattern in Figure 4.)                                                                                                       |  |  |  |  |  |

| 12   | GND   | Ground                                                                                                                                            |  |  |  |  |  |

| 13   | Vctrl | LNA gain control input: high – high gain, low – low gain. CMOS logic input with pull-down resistor as shown in Figure 9, Equivalent I/O Circuits. |  |  |  |  |  |

| 14   | GND   | Crowned                                                                                                                                           |  |  |  |  |  |

| 15   | GND   | Ground                                                                                                                                            |  |  |  |  |  |

| 16   | VCC   | Supply voltage, 3.3 V                                                                                                                             |  |  |  |  |  |

| (17) | GND   | Exposed die attach pad of the QFN package, must be soldered to ground.                                                                            |  |  |  |  |  |

### 4 Specification

#### 4.1 <u>Absolute Maximum Ratings</u>

Attempted operation outside the absolute maximum ratings of the part may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

Table 2 Absolute Maximum Ratings

| Parameter                    | Symbol            | Min  | Max                   | Unit | Condition / Remark                                          |  |  |  |

|------------------------------|-------------------|------|-----------------------|------|-------------------------------------------------------------|--|--|--|

| Supply voltage               | Vcc               |      | 3.6                   | V    | to GND                                                      |  |  |  |

| DC voltage at RF pins        | $V_{DCRF}$        | 0    | 2                     | mV   | IC provides low ohmic circuit to GND for pin RFout and RFin |  |  |  |

| Junction temperature         | Tı                |      | 150                   | °C   |                                                             |  |  |  |

| Storage temperature range    | T <sub>STG</sub>  | -65  | 150                   | °C   |                                                             |  |  |  |

| DC voltage at control inputs | V <sub>CTL</sub>  | -0.3 | V <sub>CC</sub> + 0.3 | V    | Pins Vctrl and PWR                                          |  |  |  |

| Input power into pin RFin    | P <sub>IN</sub>   |      | 0                     | dBm  |                                                             |  |  |  |

| ESD robustness, HBM          | V <sub>ESD1</sub> |      | 2000                  | V    | Note 1                                                      |  |  |  |

| ESD robustness, CDM          | V <sub>ESD2</sub> |      | 500                   | V    | Note 2                                                      |  |  |  |

Note 1 According to JEDEC JESD22-A114C Joint Standard for Electrostatic Discharge Sensitivity Testing, Human Body Model Component (HBM), Component Level

Note 2 According to JEDEC JS-002-2018 Joint Standard for Electrostatic Discharge Sensitivity Testing, Charged Device Model (CDM) - Device Level

### 4.2 **Operating Range**

Table 3 Operating Range

| Parameter                    | Symbol           | Min  | Max  | Unit | Condition / Remark |

|------------------------------|------------------|------|------|------|--------------------|

| Ambient temperature          | TA               | -40  | 85   | °C   |                    |

| Supply voltage               | Vcc              | 3.13 | 3.47 | V    | (3.3 V ± 5%)       |

| DC voltage at control inputs | V <sub>CTL</sub> | 0    | Vcc  | V    | Pins Vctrl and PWR |

Note: Do not drive input signals without power supplied to the device.

### 4.3 <u>Thermal Resistance</u>

Table 4 Thermal Resistance

| Parameter           | Symbol            | Min | Тур | Max | Unit  | Condition / Remark      |

|---------------------|-------------------|-----|-----|-----|-------|-------------------------|

| Thermal resistance, | D                 |     |     | 77  | K/W   | JEDEC Standard JESD51-5 |

| junction-to-ambient | R <sub>thja</sub> |     |     | //  | N/ VV | JEDEC Standard JESD51-5 |

### 4.4 <u>Electrical Characteristics</u>

$T_A$  = -40 °C to +85 °C unless otherwise noted. Typical values measured at  $T_A$  = 25 °C and  $V_{CC}$  = 3.3 V.

Table 5 Electrical Characteristics

| Parameter                       | Symbol               | Min                   | Тур  | Max                   | Unit | Condition / Remark             |

|---------------------------------|----------------------|-----------------------|------|-----------------------|------|--------------------------------|

| DC Parameters                   |                      |                       |      |                       |      | •                              |

| Supply current consumption      | Icc                  | 5                     | 5.6  | 6.5                   | mA   | V(Vctrl) = V(PWR) = 0          |

| Vctrl input voltage, low level  | $V_{Ctrl\_L}$        | 0                     |      | 0.3 × V <sub>CC</sub> | V    | CMOS logic input stage         |

| Vctrl input voltage, high level | $V_{Ctrl\_H}$        | 0.7 × V <sub>CC</sub> |      | Vcc                   | V    | Civios logic iliput stage      |

| PWR input voltage, low level    | $V_{PWR\_L}$         | 0                     |      | $0.2 \times V_{CC}$   | V    | DMOS input stage               |

| PWR input voltage, high level   | $V_{PWR\_H}$         | Vcc - 0.3             |      | Vcc                   | V    | PMOS input stage               |

| Logic input current, low level  | I <sub>IN_L</sub>    | -1                    |      | 1                     | μΑ   | V(Vctrl) = V(PWR) = 0          |

| Logic input current, high level | I <sub>IN_H</sub>    | 30                    | 64   | 150                   | μΑ   | V(Vctrl) = V(PWR) = 3.3 V      |

| RF Parameters                   |                      |                       |      |                       |      |                                |

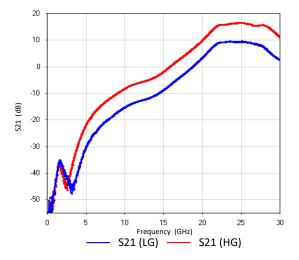

| Frequency range                 | f <sub>3dB</sub>     | 21.5                  |      | 28.7                  | GHz  |                                |

| Output impedance                | Z <sub>TXout</sub>   |                       | 50   |                       | Ω    |                                |

| Number of LNA gain settings     | N <sub>G</sub>       |                       | 2    |                       |      | controlled by input Vctrl      |

| LNA gain, high gain             | S <sub>21</sub> H    | 13.5                  | 15   | 17                    | dB   | at 24.15 GHz, V(Vctrl) = 3.3 V |

| LNA gain, low gain              | S <sub>21</sub> L    | 6.5                   | 8    | 10                    | dB   | at 24.15 GHz, V(Vctrl) = 0     |

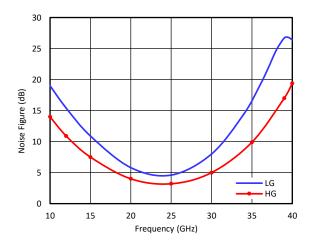

| Noise figure, high gain         | NF <sub>H</sub>      |                       | 3.2  |                       | dB   | V(Vctrl) = 3.3 V, simulated    |

| Noise figure, low gain          | NFL                  |                       | 5    |                       | dB   | V(Vctrl) = 0, simulated        |

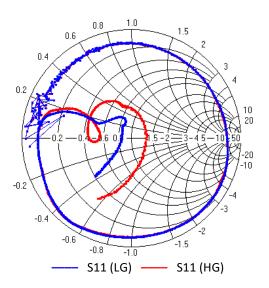

| Input return loss               | S <sub>11</sub>      | 0.3                   | 0.4  | 0.5                   |      |                                |

|                                 | Ph(S <sub>11</sub> ) | 157                   | 177  | 197                   | deg  |                                |

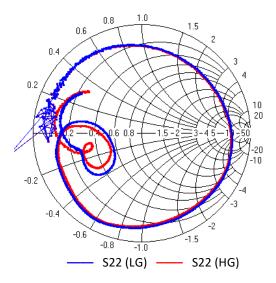

| Output return loss              | S <sub>22</sub>      | 0.4                   | 0.5  | 0.6                   |      | at 24.15 GHz                   |

|                                 | Ph(S <sub>22</sub> ) | -155                  | -140 | -125                  | deg  |                                |

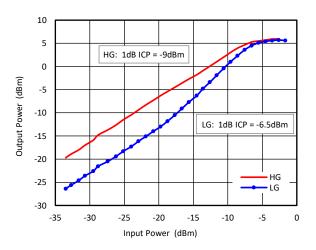

| Input Compression Point         | CPı                  | -10                   |      | -6.5                  | dBm  |                                |

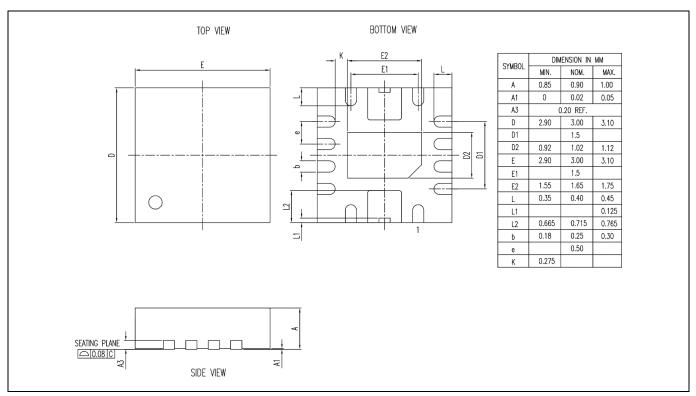

## 5 Packaging

### 5.1 Outline Dimensions

Figure 3 Outline Dimensions of QFN16, 3 mm × 3 mm, Pitch 0.5 mm

### 5.2 <u>Package Footprint</u>

Figure 4 Recommended Land Pattern

#### 5.3 Package Code

Top-Side Marking LNA005 YYWW

#### 5.4 **Qualification Test**

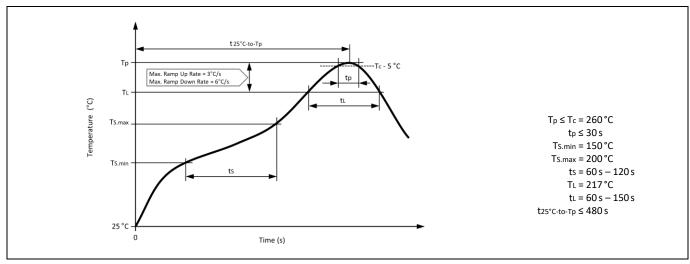

Table 6 Reliability and Environmental Test

| Qualification Test | JEDEC Standard | Condition                           | Pass / Fail |

|--------------------|----------------|-------------------------------------|-------------|

| MSL3               | J-STD-020E     | Reflow simulation 3 times at 260 °C | pass        |

Figure 5 Reflow Profile for Pb-Free Assembly according to JEDEC Standard J-STD-020E

# 6 Application

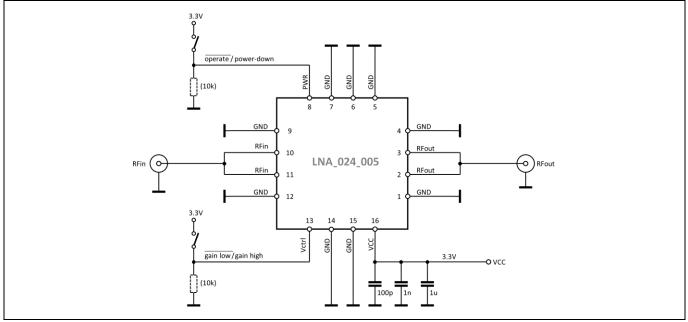

### 6.1 Application Circuit Schematic

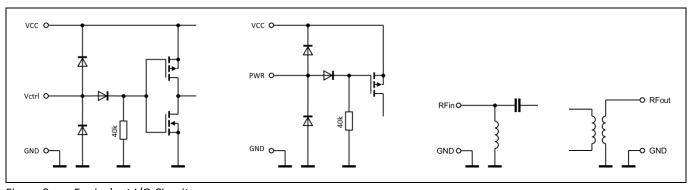

Figure 6 Application Circuit

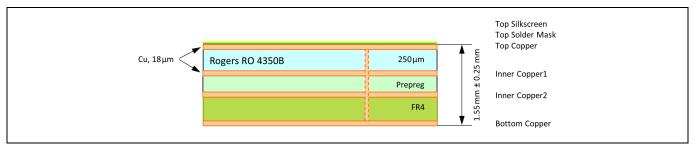

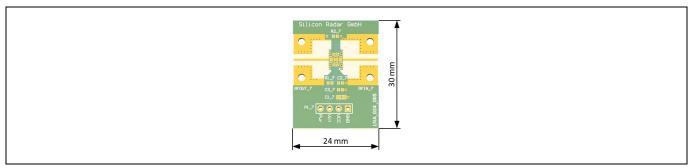

#### 6.2 <u>Evaluation Board</u>

Figure 7 Evaluation Board Stack-up

Figure 8 Evaluation Board Layout (Top View)

#### 6.3 <u>Input / Output Stages</u>

The following figures show the simplified circuits of the input and output stages. It is important that the voltage applied to the input pins should never exceed  $V_{CC}$  by more than 0.3 V. Otherwise, the supply current may be sourced through the upper ESD protection diode connected at the pin.

Figure 9 Equivalent I/O Circuits

### 7 Measurement Results

Figure 10 Input Reflection Coefficient, low and high gain

Figure 11 Output Reflection Coefficient, low and high gain

Figure 12 S21, low and high (with -30 dBm input power)

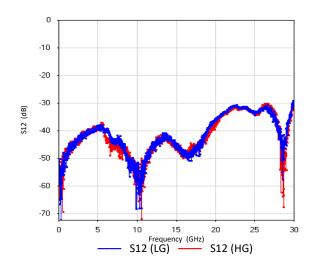

Figure 13 S12, low and high gain

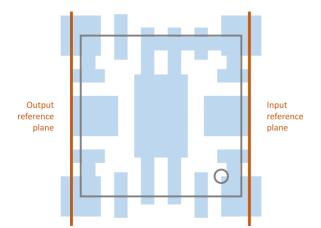

Figure 14 Reference planes for S-parameter measurement

Figure 16 Simulated Noise Figure, low and high gain

#### Disclaimer

Silicon Radar GmbH 2021. The information contained herein is subject to change at any time without notice.

Silicon Radar GmbH assumes no responsibility or liability for any loss, damage or defect of a product which is caused in whole or in part by

- (i) use of any circuitry other than circuitry embodied in a Silicon Radar GmbH product,

- (ii) misuse or abuse including static discharge, neglect, or accident,

- (iii) unauthorized modifications or repairs which have been soldered or altered during assembly and are not capable of being tested by Silicon Radar GmbH under its normal test conditions, or

- (iv) improper installation, storage, handling, warehousing, or transportation, or

- (v) being subjected to unusual physical, thermal, or electrical stress.

**Disclaimer:** Silicon Radar GmbH makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any Silicon Radar product and any product documentation. Products sold by Silicon Radar are not suitable or intended to be used in a life support applications or components, to operate nuclear facilities, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

CRITICAL USE EXCLUSION POLICY: BUYER AGREES NOT TO USE SILICON RADAR GMBH'S PRODUCTS FOR ANY APPLICATIONS OR IN ANY COMPONENTS USED IN LIFE SUPPORT DEVICES OR TO OPERATE NUCLEAR FACILITIES OR FOR USE IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

Silicon Radar GmbH owns all rights, titles and interests to the intellectual property related to Silicon Radar GmbH's products, including any software, firmware, copyright, patent, or trademark. The sale of Silicon Radar GmbH's products does not convey or imply any license under patent or other rights. Silicon Radar GmbH retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by Silicon Radar GmbH. Unless otherwise agreed to in writing by Silicon Radar GmbH, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.