# 10BASE-T1S Ethernet PHY Transceiver

# **Description**

The LAN8670/1/2 is a high-performance 10BASE-T1S single-pair Ethernet PHY transceiver for 10 Mbit/s half-duplex networking over a single pair of conductors. Utilizing standard Ethernet technology in sensor/actuator networks reduces application costs by eliminating gateways necessary with legacy networking technologies. The ability to connect multiple PHYs onto a common mixing segment further saves implementation costs by reducing cabling and switch ports. The LAN8670/1/2 is designed for use in high-reliability cost sensitive industrial, backplane, and building automation sensor/actuator applications.

### **Highlights**

- High-performance 10BASE-T1S Ethernet PHY

- Designed according to IEEE Std 802.3cg-2019

- 10 Mbit/s over single balanced pair

- Half-duplex point-to-point link segments up to at least 15m

- Half-duplex multidrop mixing segments up to at least 25m with up to at least 8 PHYs

- Media Independent Interface (MII) and Reduced Media Independent Interface (RMII)

- 2.5 MHz MII clock mode

- 50 MHz RMII clock mode

- Serial Management Interface (SMI) for rapid register access

- Comprehensive status interrupt support

- Carrier Sense Multiple Access / Collision Detection (CSMA/CD) media access control

- Physical Layer Collision Avoidance (PLCA)

- Allows for high bandwidth utilization by avoiding collisions on the physical layer

- Burst mode for transmission of multiple packets for high packet rate latency-sensitive applications

- Enhanced electromagnetic compatibility / electromagnetic interference (EMC/EMI) performance

- Low RF emissions

- Robust against injected currents and network cable shorts to ground or battery

- Simple low cost analog front-end

- Single 3.3V supply with integrated 1.8V regulator

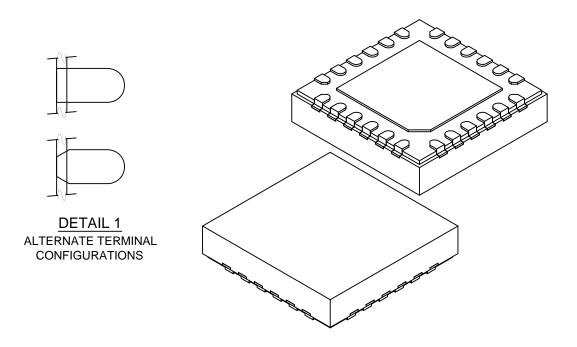

- Small footprint VQFN packaging with wettable flanks

- LAN8670 32-pin (5 x 5 mm)

- LAN8671 24-pin (4 x 4 mm)

- LAN8672 36-pin (6 x 6 mm)

- -40°C to +125°C extended temperature range

- Microchip Functional Safety Ready

### **Target Applications**

- Sensor/actuator networks operating at high bandwidth

- Microphone networks delivering audio streams for beamforming, hands-free microphones, etc.

- Backplane communication

- · Industrial control cabinets and machine control

- · Building automation

## To Our Valued Customers

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com or fax the Reader Response Form in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

**Datasheet** DS60001573C-page 2 © 2021 Microchip Technology Inc.

# Conformity

Table 1 shows the conformity relationship between data sheet, silicon, and product revisions. This data sheet applies to silicon revision 2 (0010b) as shown below.

**Table 1. Conformity Table**

| Product Revision <u>1</u> | Silicon Revision <sup>2</sup> | Data Sheet Revision |

|---------------------------|-------------------------------|---------------------|

| A0                        | Rev 0 (0000b)                 | DS60001573A         |

| B1                        | Rev 2 (0010b)                 | DS60001573B         |

| B1                        | Rev 2 (0010b)                 | DS60001573C         |

#### Notes:

- 1. The product revision is noted in the package top marking.

- 2. The silicon revision is obtained by reading the Manufacturer's Model Revision from the PHY Identifier 1 register.

#### **Related Links**

9. Package Marking Information

5.1.4 PHY\_ID1

# **Table of Contents**

| Des | scriptio | on                                                 | 1  |

|-----|----------|----------------------------------------------------|----|

| То  | Our Va   | alued Customers                                    | 2  |

| Cor | nformit  | ty                                                 | 3  |

| 1.  | Prefa    | ice                                                | 6  |

|     | 1.1.     | General Terms                                      | 6  |

|     | 1.2.     | Buffer Types                                       |    |

|     | 1.3.     | Register Bit Types                                 |    |

|     | 1.4.     | Reference Documents                                | 8  |

| 2.  | Intro    | duction                                            | 9  |

|     | 2.1.     | General Description                                | 9  |

| 3.  | Pin D    | Description and Configuration                      | 11 |

|     | 3.1.     | LAN8670 Pin Assignments                            | 11 |

|     | 3.2.     | LAN8671 Pin Assignments                            | 13 |

|     | 3.3.     | LAN8672 Pin Assignments                            | 14 |

|     | 3.4.     | Pin Descriptions                                   | 16 |

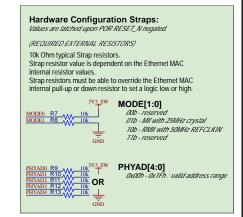

|     | 3.5.     | Configuration Straps                               | 18 |

| 4.  | Func     | tional Descriptions                                | 20 |

|     | 4.1.     | Media Independent Interface (MII)                  | 20 |

|     | 4.2.     | Reduced Media Independent Interface (RMII)         | 20 |

|     | 4.3.     | Serial Management Interface (SMI)                  | 21 |

|     | 4.4.     | Interrupt Management                               | 22 |

|     | 4.5.     | Resets                                             | 23 |

|     | 4.6.     | Power Management                                   | 24 |

|     | 4.7.     | Initialization                                     |    |

|     | 4.8.     | Clock Manager                                      |    |

|     | 4.9.     | Physical Layer Collision Avoidance (PLCA)          | 25 |

| 5.  | Regis    | ster Descriptions                                  | 28 |

|     | 5.1.     | 5                                                  |    |

|     | 5.2.     | PMA/PMD Registers                                  | 40 |

|     | 5.3.     | PCS Registers                                      |    |

|     | 5.4.     | Miscellaneous Registers                            | 51 |

| 6.  | Appli    | cation Information                                 | 73 |

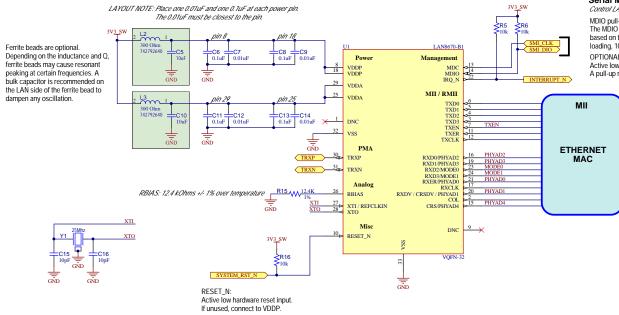

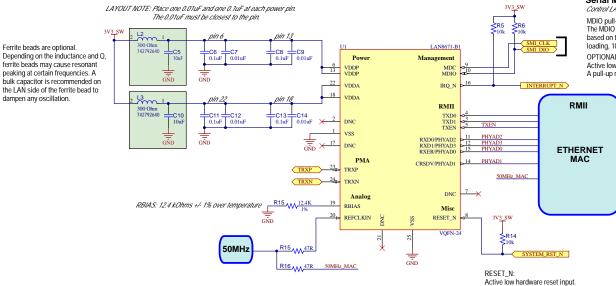

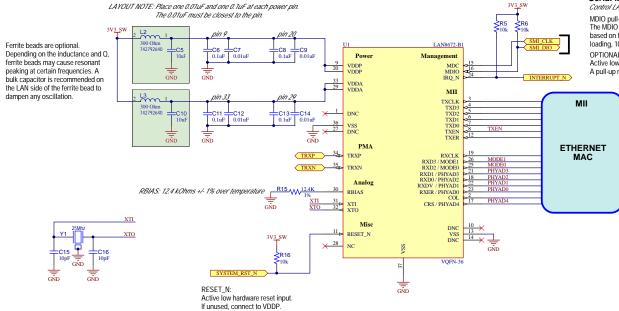

|     | 6.1.     | MII Operation                                      | 73 |

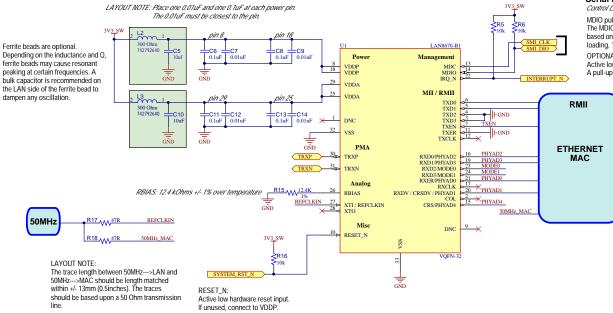

|     | 6.2.     | RMII Operation with Reference Clock                | 73 |

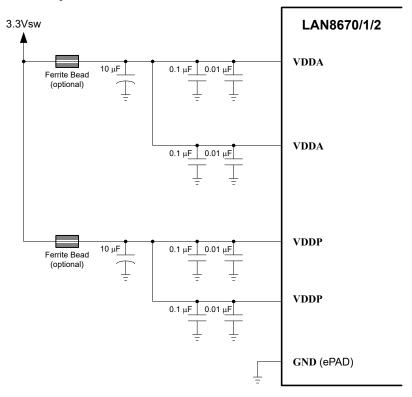

|     | 6.3.     | Power Connectivity                                 | 74 |

|     | 6.4.     | Crystal Oscillator Selection                       | 75 |

|     | 6.5.     | Electromagnetic Compatibility (EMC) Considerations | 76 |

|     | 6.6.     | Reference Schematics                               | 76 |

| 7.  | Oper     | ational Characteristics                            | 81 |

|      | 7.1.     | Absolute Maximum Ratings                      | 81   |

|------|----------|-----------------------------------------------|------|

|      | 7.2.     | Operating Conditions                          | 82   |

|      | 7.3.     | Power Consumption                             | 82   |

|      | 7.4.     | Package Thermal Specifications                | 83   |

|      | 7.5.     | DC Specifications (other than 10BASE-T1S PMA) | 84   |

|      | 7.6.     | AC Specifications                             | 86   |

|      | 7.7.     | 10BASE-T1S PMA                                | 91   |

|      | 7.8.     | Clock Circuit                                 | 92   |

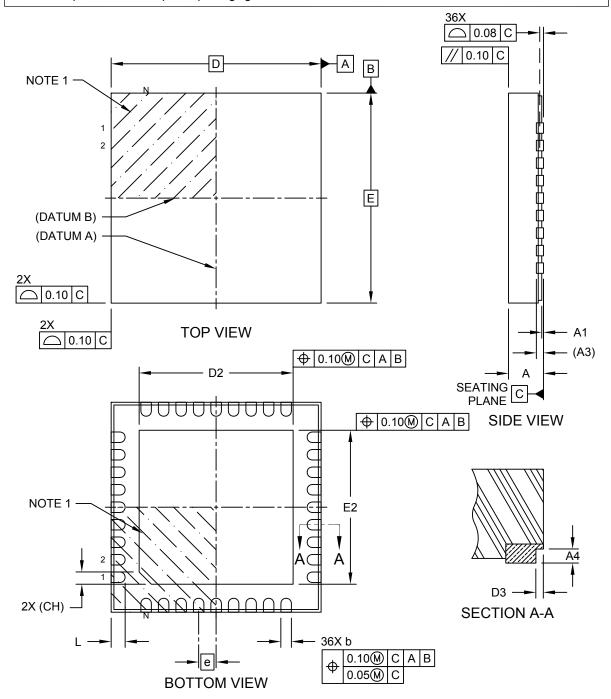

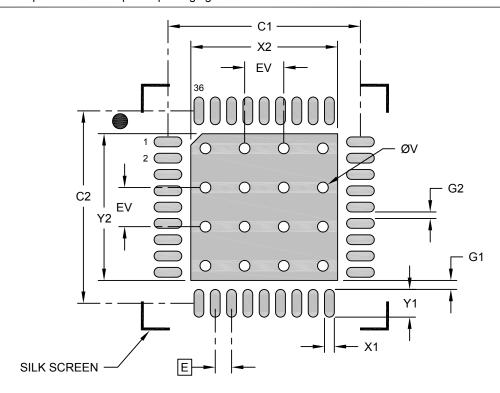

| 8.   | Packa    | ging Information                              | 93   |

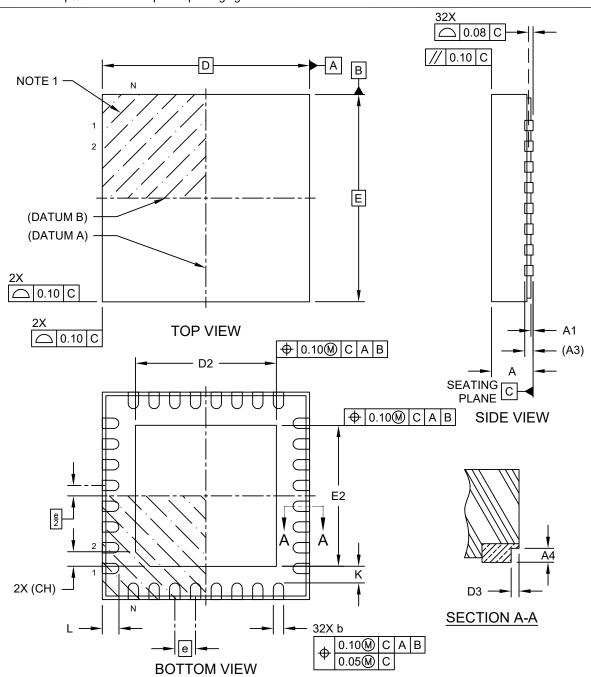

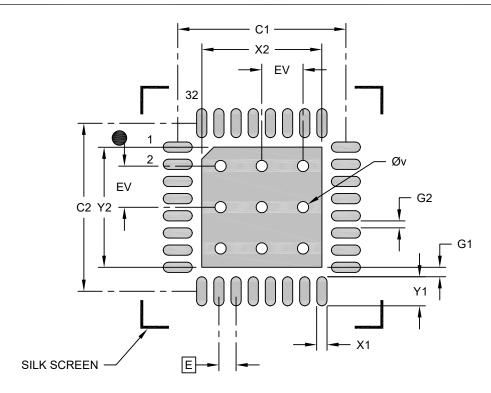

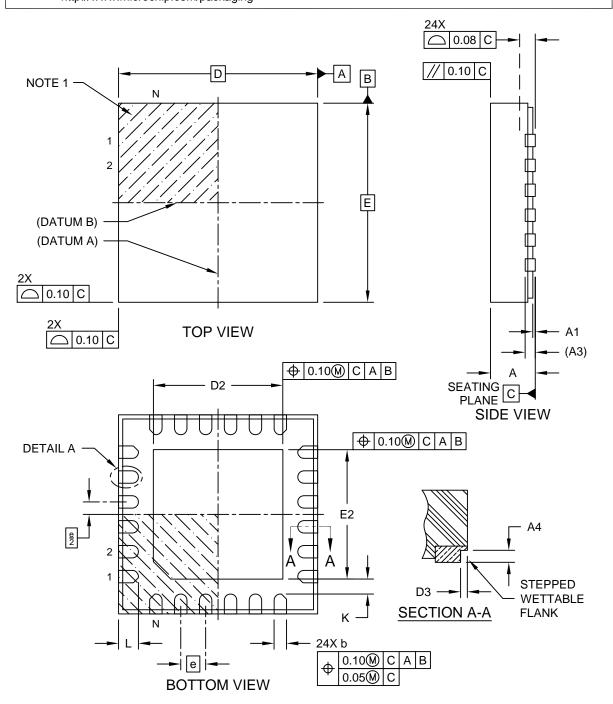

|      | 8.1.     | 32-VQFN (LAN8670 Only)                        | 93   |

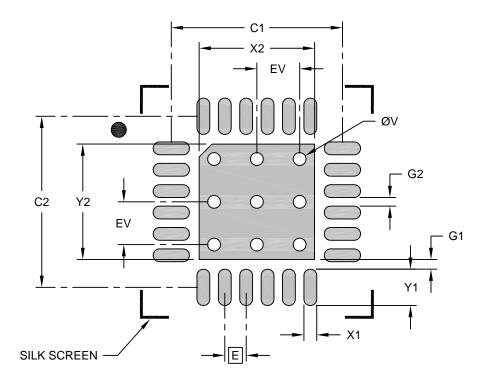

|      | 8.2.     | 24-VQFN (LAN8671 Only)                        | 96   |

|      | 8.3.     | 36-VQFN (LAN8672 Only)                        | 99   |

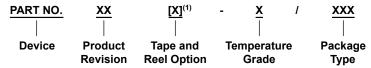

| 9.   | Packa    | ge Marking Information                        | 102  |

| 10.  | Data S   | Sheet Revision History                        | 104  |

| The  | Micro    | chip Website                                  | 105  |

| Pro  | duct C   | nange Notification Service                    | .105 |

| Cus  | stomer   | Support                                       | 105  |

| Pro  | duct Id  | entification System                           | 106  |

| Mic  | rochip   | Devices Code Protection Feature               | 107  |

| Leg  | al Noti  | ce                                            | 107  |

| Tra  | demark   | S                                             | 107  |

| Qua  | ality Ma | nagement System                               | 108  |

| ۱۸۷۵ | rldwida  | Calca and Camina                              | 100  |

# 1. Preface

# 1.1 General Terms

# Table 1-1. General Terms

| Term       | Description                                                                                   |  |

|------------|-----------------------------------------------------------------------------------------------|--|

| 10BASE-T   | 10 Mbit/s Ethernet over twisted pair, IEEE Std 802.3 <sup>™</sup> Clause 14                   |  |

| 10BASE-T1L | 10 Mbit/s Ethernet over long-reach single pair of conductors, IEEE Std 802.3 Clause 146       |  |

| 10BASE-T1S | 10 Mbit/s Ethernet over short-reach single pair of conductors, IEEE Std 802.3 Clause 147      |  |

| CSMA/CD    | Carrier Sense Multiple Access with Collision Detection                                        |  |

| CSR        | Control and Status Register                                                                   |  |

| ВТ         | Bit Time, 100 ns for 10 Mbps Ethernet                                                         |  |

| LDO        | Low Dropout Regulator                                                                         |  |

| MAC        | Media Access Controller                                                                       |  |

| MDI        | Medium Dependent Interface                                                                    |  |

| MII        | Media Independent Interface, IEEE Std 802.3 Clause 22                                         |  |

| PCS        | Physical Coding Sublayer                                                                      |  |

| PLCA       | Physical Layer Collision Avoidance, IEEE Std 802.3 Clause 148                                 |  |

| PMA        | Physical Medium Attachment sublayer                                                           |  |

| PMD        | Physical Medium Dependent sublayer                                                            |  |

| POR        | Power-on Reset                                                                                |  |

| RS         | Reconciliation Sublayer                                                                       |  |

| SMI        | Serial Management Interface, also known as MII Management Interface, IEEE Std 802.3 Clause 22 |  |

| STA        | Station management entity                                                                     |  |

| RMII       | Reduced Media Independent Interface                                                           |  |

# 1.2 Buffer Types

Table 1-2. LAN8670/1/2 Buffer Type Descriptions

| Buffer   | Description                                                                                                                                                                                                                                                                                                                                                         |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Al       | Analog input                                                                                                                                                                                                                                                                                                                                                        |  |

| AO       | Analog output                                                                                                                                                                                                                                                                                                                                                       |  |

| AIO      | Analog bi-directional                                                                                                                                                                                                                                                                                                                                               |  |

| ICLK     | Oscillator input                                                                                                                                                                                                                                                                                                                                                    |  |

| OCLK     | Crystal oscillator output                                                                                                                                                                                                                                                                                                                                           |  |

| Р        | Power                                                                                                                                                                                                                                                                                                                                                               |  |

| PD       | 55 kΩ (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.  Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added. |  |

| PU       | 55 kΩ (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled. Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added.       |  |

| VIS-VDDP | 3.3V Schmitt-triggered input (VDDP power domain)                                                                                                                                                                                                                                                                                                                    |  |

| VO-VDDP  | 3.3V output (VDDP power domain)                                                                                                                                                                                                                                                                                                                                     |  |

| VOH-VDDP | 3.3V high-speed output (VDDP power domain)                                                                                                                                                                                                                                                                                                                          |  |

| VOD-VDDP | 3.3V open-drain output (VDDP power domain)                                                                                                                                                                                                                                                                                                                          |  |

Note: Digital signals are not 5V tolerant unless specified.

# 1.3 Register Bit Types

The following table describes the register bit attributes used throughout this document.

Table 1-3. Register Bit Types

| Register Bit Type<br>Notation | Register Bit Description                                                                                                                                                                           |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R                             | Read: A register or bit with this attribute can be read.                                                                                                                                           |  |

| W                             | Write: A register or bit with this attribute can be written.                                                                                                                                       |  |

| RO                            | Read Only: A register of bit with this attribute is read only; writing has no effect.                                                                                                              |  |

| WO                            | Write Only: If a register or bit is write-only, reads will return unspecified data.                                                                                                                |  |

| W1S                           | Write One to Set: Writing a one sets the value. Writing a zero has no effect.                                                                                                                      |  |

| W1C                           | Write One to Clear: Writing a one clears the value. Writing a zero has no effect.                                                                                                                  |  |

| WAC                           | Write Anything to Clear: Writing anything clears the value.                                                                                                                                        |  |

| RC                            | Read to Clear: Content is cleared after the read. Writes have no effect.                                                                                                                           |  |

| SC                            | <b>Self Clearing:</b> A bit with this attribute will be cleared to '0' after being written as '1'. Hardware often clears such bits following the completion of some action initiated by the write. |  |

| NASR                          | Not Affected by Software Reset: The state of NASR bits do not change on assertion of a software reset.                                                                                             |  |

| STKY                          | This field is "Sticky" in that it is neither initialized nor modified by hot reset or Function Level Reset.                                                                                        |  |

| RESERVED                      | <b>Reserved Field:</b> Reserved fields must be written with the same default values as specified. The value of reserved bits is not guaranteed on a read.                                          |  |

Many of these register bit notations can be combined. Some examples of this are:

- R/W: Can be written. Will return current setting on a read.

- R/W1C: Will return current setting on a read. Writing a '1' clears the bit.

### 1.4 Reference Documents

- 1. IEEE Std 802.3<sup>™</sup>-2018, IEEE Standard for Ethernet. standards.ieee.org/standard/802\_3-2018.html

- 2. IEEE Std 802.3cg<sup>™</sup>-2019, IEEE Standard for Ethernet, Amendment 5: Physical Layer Specifications and Management Parameters for 10 Mb/s Operation and Associated Power Delivery over a Single Balanced Pair of Conductors.

- standards.ieee.org/standard/802\_3cg-2019.html

- 3. RMII Specification Revision 1.2.

# 2. Introduction

# 2.1 General Description

The Microchip LAN8670/1/2 is a compact, low power, and cost-effective single-port 10BASE-T1S Ethernet physical layer transceiver designed according to the IEEE Std 802.3cg-2019 specification. The device provides 10 Mbit/s half-duplex transmit and receive capability over single-balanced pair medium such as Unshielded Twisted Pair (UTP) cable. The LAN8670/1/2 is designed for use in applications requiring extended temperature range (-40°C to +125°C). The device is also compliant to industrial EMC and EMI requirements. The single power supply and simple analog front end simplifies its integration into small form factor applications.

The LAN8670/1/2 allows for the creation of both multidrop and point-to-point network topologies. Point-to-point link segments of up to at least 15m in length are supported. The multidrop mode supports up to at least 8 PHYs connected to a common mixing segment of up to at least 25m in length. The ability to connect multiple PHYs to a common mixing segment reduces weight and implementation costs by reducing cabling and switch ports.

The LAN8670/1/2 supports communication with an Ethernet MAC via standard MII/RMII interfaces. An integrated serial management interface (SMI) provides rapid register access and configuration at up to 4 MHz.

Access to the physical medium is managed by CSMA/CD and optionally supplemented by Physical Layer Collision Avoidance (PLCA).

The LAN8670/1/2 is designed to be used in functional safety related applications.

The Microchip LAN8670/1/2 family includes the following devices:

- LAN8670

- LAN8671

- LAN8672

Device specific features that do not pertain to the entire LAN8670/1/2 family are called out independently throughout this document. Table 2-1 below provides a summary of the feature differences between family members.

Table 2-1. LAN8670/1/2 Family Feature Matrix

| Part Number | Package | MII Support | RMII Support | PLCA Support | -40 <sup>0</sup> to +125 <sup>0</sup> C |

|-------------|---------|-------------|--------------|--------------|-----------------------------------------|

| LAN8670     | 32-VQFN | X           | X            | X            | X                                       |

| LAN8671     | 24-VQFN |             | X            | X            | X                                       |

| LAN8672     | 36-VQFN | X           |              | X            | X                                       |

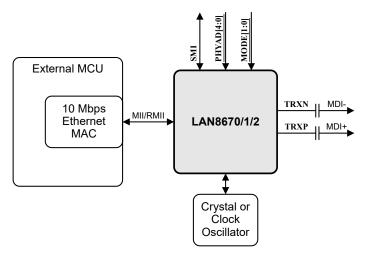

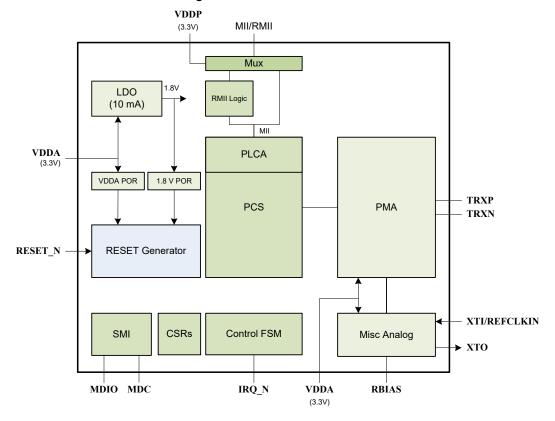

A system-level block diagram and internal block diagram of the LAN8670/1/2 are shown in the following figures.

Figure 2-1. LAN8670/1/2 System-Level Block Diagram

Figure 2-2. LAN8670/1/2 Internal Block Diagram

# 3. Pin Description and Configuration

The pin assignments and descriptions for the LAN8670/1/2 are detailed in the following sections. Pin buffer type definitions are detailed in the Buffer Types section.

#### **Related Links**

1.2 Buffer Types

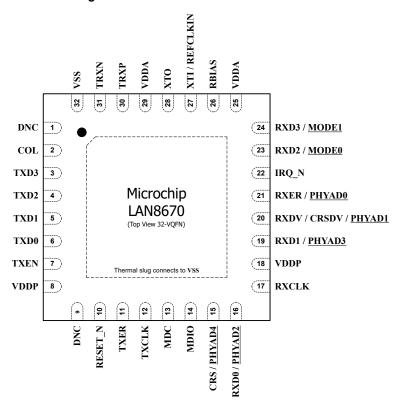

# 3.1 LAN8670 Pin Assignments

Figure 3-1. LAN8670 32-VQFN Pin Assignments

Note: Exposed pad (VSS) on bottom of package must be connected to ground.

**Note:** Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor.

Table 3-1. LAN8670 32-VQFN Pin Assignments

| Pin Num | Pin Name            | Pin Num | Pin Name          |

|---------|---------------------|---------|-------------------|

| 1       | DNC                 | 17      | RXCLK             |

| 2       | COL                 | 18      | VDDP              |

| 3       | TXD3                | 19      | RXD1/PHYAD3       |

| 4       | TXD2                | 20      | RXDV/CRSDV/PHYAD1 |

| 5       | TXD1                | 21      | RXER/PHYAD0       |

| 6       | TXD0                | 22      | IRQ_N             |

| 7       | TXEN                | 23      | RXD2/MODE0        |

| 8       | VDDP                | 24      | RXD3/MODE1        |

| 9       | DNC                 | 25      | VDDA              |

| 10      | RESET_N             | 26      | RBIAS             |

| 11      | TXER                | 27      | XTI/REFCLKIN      |

| 12      | TXCLK               | 28      | ХТО               |

| 13      | MDC                 | 29      | VDDA              |

| 14      | MDIO                | 30      | TRXP              |

| 15      | CRS/ <u>PHYAD4</u>  | 31      | TRXN              |

| 16      | RXD0/ <u>PHYAD2</u> | 32      | VSS               |

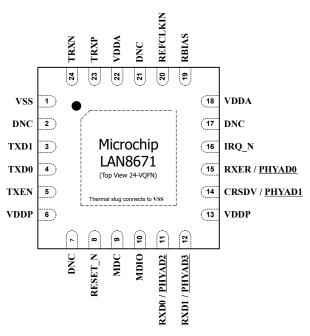

# 3.2 LAN8671 Pin Assignments

Figure 3-2. LAN8671 24-VQFN Pin Assignments

Note: Exposed pad (VSS) on bottom of package must be connected to ground.

**Note:** Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor.

Table 3-2. LAN8671 24-VQFN Pin Assignments

| in Num | Pin Name    | Pin Num | Pin Name     |

|--------|-------------|---------|--------------|

| 1      | VSS         | 13      | VDDP         |

| 2      | DNC         | 14      | CRSDV/PHYAD1 |

| 3      | TXD1        | 15      | RXER/PHYAD0  |

| 4      | TXD0        | 16      | IRQ_N        |

| 5      | TXEN        | 17      | DNC          |

| 6      | VDDP        | 18      | VDDA         |

| 7      | DNC         | 19      | RBIAS        |

| 8      | RESET_N     | 20      | REFCLKIN     |

| 9      | MDC         | 21      | DNC          |

| 10     | MDIO        | 22      | VDDA         |

| 11     | RXD0/PHYAD2 | 23      | TRXP         |

| 12     | RXD1/PHYAD3 | 24      | TRXN         |

# 3.3 LAN8672 Pin Assignments

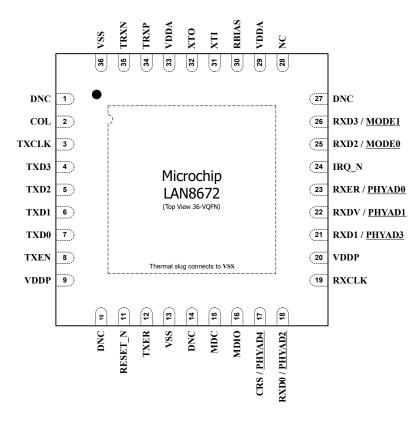

# Figure 3-3. LAN8672 36-VQFN Pin Assignments

$\textbf{Note:} \ \text{Exposed pad (VSS)} \ \text{on bottom of package must be connected to ground.}$

**Note:** Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor.

Table 3-3. LAN8672 36-VQFN Pin Assignments

| n Num | Pin Name           | Pin Num | Pin Name            |

|-------|--------------------|---------|---------------------|

| 1     | DNC                | 19      | RXCLK               |

| 2     | COL                | 20      | VDDP                |

| 3     | TXCLK              | 21      | RXD1/ <u>PHYAD3</u> |

| 4     | TXD3               | 22      | RXDV/ <u>PHYAD1</u> |

| 5     | TXD2               | 23      | RXER/PHYAD0         |

| 6     | TXD1               | 24      | IRQ_N               |

| 7     | TXD0               | 25      | RXD2/MODE0          |

| 8     | TXEN               | 26      | RXD3/MODE1          |

| 9     | VDDP               | 27      | DNC                 |

| 10    | DNC                | 28      | NC                  |

| 11    | RESET_N            | 29      | VDDA                |

| 12    | TXER               | 30      | RBIAS               |

| 13    | VSS                | 31      | XTI                 |

| 14    | DNC                | 32      | ХТО                 |

| 15    | MDC                | 33      | VDDA                |

| 16    | MDIO               | 34      | TRXP                |

| 17    | CRS/ <u>PHYAD4</u> | 35      | TRXN                |

| 18    | RXD0/PHYAD2        | 36      | VSS                 |

# 3.4 Pin Descriptions

This section contains descriptions of the various LAN8670/1/2 pins. The "\_N" symbol in the signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. For example, RESET\_N indicates that the reset signal is active low. When "\_N" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

Pin buffer type definitions are detailed in the Buffer Types section.

Table 3-4. MII/RMII Signals

| Name                         | Symbol | Buffer Type | Description                                                                                                                                                                                        |

|------------------------------|--------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit Data 0              | TXD0   | VIS-VDDP    | Transmit data bus bit 0 (all modes)                                                                                                                                                                |

| Transmit Data 1              | TXD1   | VIS-VDDP    | Transmit data bus bit 1 (all modes)                                                                                                                                                                |

| Transmit Data 2              | TXD2   | VIS-VDDP    | Transmit data bus bit 2 (MII mode)                                                                                                                                                                 |

| (MII Mode)                   |        |             | In RMII mode, this signal is not used and is internally pulled-down to VSS.                                                                                                                        |

| Transmit Data 3              | TXD3   | VIS-VDDP    | Transmit data bus bit 3 (MII mode)                                                                                                                                                                 |

| (MII Mode)                   |        |             | In RMII mode, this signal is not used and is internally pulled-down to VSS.                                                                                                                        |

| Transmit Error<br>(MII Mode) | TXER   | VIS-VDDP    | This signal is asserted to indicate that an error was detected somewhere in the packet presently being transferred to the transceiver.                                                             |

|                              |        |             | This pin is unused in RMII mode and should be connected to VSS.                                                                                                                                    |

| Transmit Enable              | TXEN   | VIS-VDDP    | Indicates that valid transmission data is present on TXD[3:0]. In RMII mode, only TXD[1:0] provide valid data.                                                                                     |

|                              |        |             | <b>Note:</b> A pull-down resistor is recommended to prevent incidental transmission if the MAC does not actively pull-down or drive this pin low at all times during its reset and initialization. |

| Transmit Clock<br>(MII Mode) | TXCLK  | VO-VDDP     | 2.5 MHz clock used to latch data from the MAC into the transceiver.                                                                                                                                |

|                              |        |             | In RMII mode, this pin is unused and is driven low. It should be left unconnected.                                                                                                                 |

| Receive Data 0               | RXD0   | VOH-VDDP    | Receive data bus bit 0 (all modes)                                                                                                                                                                 |

| Receive Data 1               | RXD1   | VOH-VDDP    | Receive data bus bit 1 (all modes)                                                                                                                                                                 |

| Receive Data 2               | RXD2   | VO-VDDP     | Receive data bus bit 2 (MII mode)                                                                                                                                                                  |

| (MII Mode)                   |        |             | In RMII mode, this pin is unused and is driven low.                                                                                                                                                |

| Receive Data 3               | RXD3   | VO-VDDP     | Receive data bus bit 3 (MII mode)                                                                                                                                                                  |

| (MII Mode)                   |        |             | In RMII mode, this pin is unused and is driven low.                                                                                                                                                |

| Receive Error                | RXER   | VOH-VDDP    | This signal is asserted to indicate that an error was detected somewhere in the packet presently being transferred from the transceiver.                                                           |

|                              |        |             | This signal is optional in RMII mode.                                                                                                                                                              |

| continued                                         |        |             |                                                                                                                                                |  |

|---------------------------------------------------|--------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name                                              | Symbol | Buffer Type | Description                                                                                                                                    |  |

| Receive Data Valid<br>(MII Mode)                  | RXDV   | VOH-VDDP    | Indicates that recovered and decoded data is available on the RXD[3:0] pins.  This signal is not used in RMII mode.                            |  |

| Receive Clock<br>(MII Mode)                       | RXCLK  | VO-VDDP     | In MII mode, this pin is the 2.5 MHz receive clock output.  In RMII mode, this pin is unused and is driven low. It should be left unconnected. |  |

| Carrier Sense / Receive Data<br>Valid (RMII Mode) | CRSDV  | VOH-VDDP    | This signal is asserted to indicate the receive medium is non-idle in RMII mode.  This signal is not used in MII mode.                         |  |

| Collision Detect<br>(MII Mode)                    | COL    | VO-VDDP     | Collision Detect.  In RMII mode, this pin is unused and is driven low.                                                                         |  |

| Carrier Sense<br>(MII Mode)                       | CRS    | VO-VDDP     | Carrier Sense.  In RMII mode, this pin is unused and is driven low.                                                                            |  |

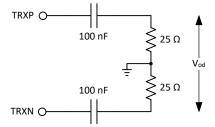

### **Table 3-5. Ethernet Transceiver Pins**

| Name                             | Symbol | Buffer Type | Description                                    |

|----------------------------------|--------|-------------|------------------------------------------------|

| Ethernet TX/RX Positive Terminal | TRXP   | AIO         | Positive terminal for transmit/receive signal. |

| Ethernet TX/RX Negative Terminal | TRXN   | AIO         | Negative terminal for transmit/receive signal. |

# Table 3-6. Serial Management Interface (SMI) Pins

| Name                  | Symbol | Buffer Type | Description                                    |

|-----------------------|--------|-------------|------------------------------------------------|

| SMI Data Input/Output | MDIO   | VIS-VDDP /  | Serial Management Interface data input/output. |

|                       |        | VO-VDDP     |                                                |

| SMI Clock             | MDC    | VIS-VDDP    | Serial Management Interface clock.             |

## Table 3-7. Miscellaneous Pins

| Name                           | Symbol   | Buffer Type | Description                                                                                                                                                                                                                              |

|--------------------------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External 25 MHz Crystal Input  | XTI      | ICLK        | External 25 MHz crystal input.                                                                                                                                                                                                           |

| External Clock Input           | REFCLKIN | ICLK        | Single-ended clock oscillator input. A frequency of 25 MHz shall be used in all modes except RMII, which requires 50 MHz.  Note: When using a single-ended clock oscillator, XTO must be left unconnected with <10 pF stray capacitance. |

| External 25 MHz Crystal Output | ХТО      | OCLK        | External 25 MHz crystal output.  Note: When using a single-ended clock oscillator on XTI/ REFCLKIN, this pin must be left unconnected with <10 pF stray capacitance.                                                                     |

| Interrupt                      | IRQ_N    | VOD-VDDP    | Device interrupt. Active low and open drain.<br><b>Note:</b> When used, this pin requires a $10 \text{ k}\Omega$ (typical) pull-up to VDDP.<br><b>Note:</b> This pin is to be unconnected when unused.                                   |

| System Reset                   | RESET_N  | VIS-VDDP    | System reset. This pin is active low. If unused, this pin must be pulled-up to VDDP.                                                                                                                                                     |

| continued      |        |             |                                                                                                                                                                                                                                     |

|----------------|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name           | Symbol | Buffer Type | Description                                                                                                                                                                                                                         |

| Bias Resistor  | RBIAS  | AIO         | External bias resistor connection pin. This pin requires connection of a 12.4 k $\Omega$ resistor to ground.<br><b>Note:</b> The resistor must be within $\pm$ 1% tolerance across the entire expected operating temperature range. |

| Do Not Connect | DNC    | -           | Pin is internally connected. The pin must be left floating externally.                                                                                                                                                              |

| No Connect     | NC     | -           | Pin is not connected internally. The pin should be left floating externally.                                                                                                                                                        |

### Table 3-8. Configuration Straps

| Name                                       | Symbol     | Buffer Type | Description                                                                                                                                             |

|--------------------------------------------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Mode Configuration<br>Straps 1-0 | MODE[1:0]  | VIS-VDDP    | These configuration straps are used to select the device's default mode of operation. See Section 3.5, Configuration Straps for additional information. |

| PHY Address Configuration<br>Straps 4-0    | PHYAD[4:0] | VIS-VDDP    | These configuration straps are used to select the device's default PHY SMI address. See Section 3.5, Configuration Straps for additional information.   |

#### Table 3-9. Power Pins

| Name                                        | Symbol | Buffer Type | Description                                                                              |

|---------------------------------------------|--------|-------------|------------------------------------------------------------------------------------------|

| +3.3V Switched I/O Power Supply Input       | VDDP   | Р           | +3.3V switched I/O power supply input.                                                   |

| +3.3V Switched Analog Power<br>Supply Input | VDDA   | Р           | +3.3V switched analog power supply input.                                                |

| Ground                                      | VSS    | Р           | Common ground.  This exposed pad must be connected to the ground plane with a via array. |

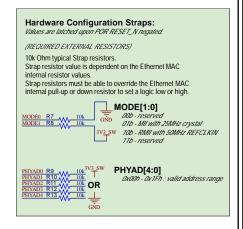

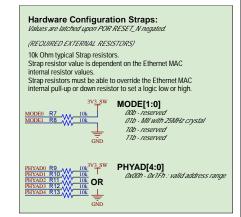

# 3.5 Configuration Straps

Configuration straps allow various features of the device to be automatically configured to user defined values. Configuration straps are identified by an underlined symbol name in the pin assignment lists and are latched on Power-On Reset (POR) and pin reset (RESET\_N). Configuration straps do not have internal resistors to prevent the signal from floating when unconnected.

**Important:** External pull-up or pull-down resistors must be sized appropriately (10 k $\Omega$ , typical) to ensure that the configuration straps reach the required voltage level prior to latching at reset.

### 3.5.1 Device Mode (MODE[1:0])

The MODE[1:0] configuration straps control various device modes. When the RESET\_N pin is negated, the associated register bit values are loaded according to the MODE[1:0] configuration straps and the device is configured. When a soft reset occurs via the Soft Reset bit of the Basic Control Register, the configuration of the device is controlled by the register bit values and the MODE[1:0] configuration straps have no affect.

The device's mode may be configured using the hardware configuration straps as summarized in Table 3-10 below.

Note: As the LAN8672 only supports operation in MII mode, the MODE[1:0] configuration straps must be set to 01b.

### Table 3-10. MODE[1:0] Configuration Straps

| MODE[1:0] | Definition                                      |

|-----------|-------------------------------------------------|

| 00b       | Reserved                                        |

| 01b       | PHY is placed in MII mode with 25 MHz crystal   |

| 10b       | PHY is placed in RMII mode with 50 MHz REFCLKIN |

| 11b       | Reserved                                        |

### 3.5.2 PHY Address (PHYAD[4:0])

The PHYAD[4:0] configuration straps are driven high or low to give each PHY a unique SMI address. This address is latched into an internal register at the end of a hardware reset. In a multi-transceiver application (such as a switch), the controller is able to manage each transceiver via the unique address. Each transceiver checks each management data frame for a matching address in the relevant bits. When a match is recognized, the transceiver responds to that particular frame.

The LAN8670/2 SMI address must be configured using the <u>PHYAD[4:0]</u> hardware configuration straps to any value between 0x00 and 0x1F. The LAN8671 SMI address must be configured using the <u>PHYAD[3:0]</u> hardware configuration straps to any value between 0x00 and 0x0F.

# 4. Functional Descriptions

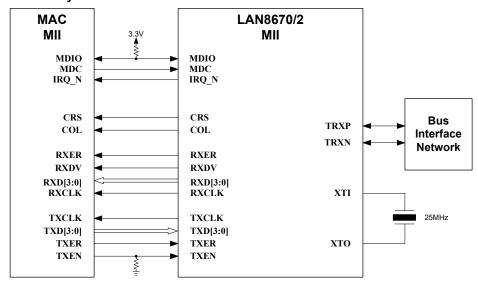

## 4.1 Media Independent Interface (MII)

The integrated Media Independent Interface (MII) provides a common interface between physical layer and MAC layer devices, adhering to IEEE Std 802.3-2018 *IEEE Standard for Ethernet*.

The MII includes the following interface signals:

- Transmit Data TXD[3:0]

- · Transmit Enable TXEN

- · Transmit Clock TXCLK

- · Transmit Error TXER

- · Receive Data RXD[3:0]

- · Receive Data Valid RXDV

- Receive Clock RXCLK

- · Receive Error RXER

- · Carrier Sense CRS

- Collision Detect COL

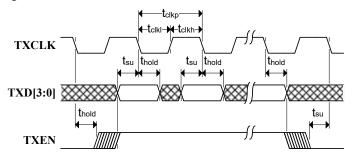

In MII mode, on the transmit path, the transceiver drives the transmit clock, TXCLK, to the controller. The controller synchronizes the transmit data to the rising edge of TXCLK and drives TXEN high to indicate valid transmit data on TXD[3:0]. The transceiver will synchronously capture TXEN, TXER, and TXD[3:0] on the falling edge of TXCLK.

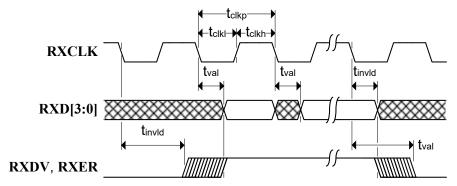

On the receive path, the transceiver drives both the receive data, RXD[3:0], and the receive clock, RXCLK. The controller captures in the receive data on the rising edge of RXCLK when the transceiver drives RXDV high. The transceiver drives RXER high when a receive error is detected (e.g., an uncorrectable decoding error). The transceiver synchronizes RXD[3:0], RXDV, and RXER to change on the falling edge of RXCLK.

The CRS and COL signals are asserted asynchronously to the clocks.

For timing information, refer to the MII Timing section. Refer to Clause 22 of the IEEE Std 802.3-2018 IEEE Standard for Ethernet specification for additional MII information.

**Note:** Many modern controllers, often found on switches, implement a reduced pin MII assuming full-duplex point-to-point operation. These interfaces, known as MII-Lite, do not include the required CRS and COL signals for 10BASE-T1S half-duplex operation. Back-to-back connection of two half-duplex transceivers is also not supported due to the CRS and COL requirement.

**Note:** The connection of a  $10 \text{ k}\Omega$  pull-down resistor on TXEN is recommended to prevent incidental transmission if the MAC does not actively pull-down or drive this pin low at all times during its reset and initialization.

#### **Related Links**

7.6.6 MII Timing

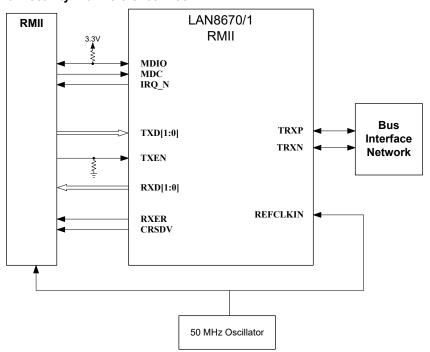

# 4.2 Reduced Media Independent Interface (RMII)

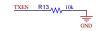

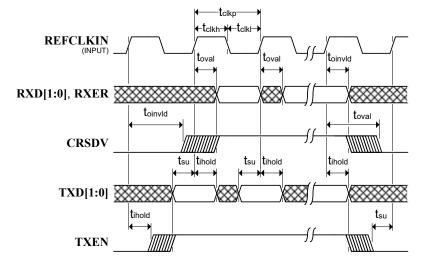

The integrated Reduced Media Independent Interface (RMII) provides a common low pin count interface between the physical layer and MAC layer devices, adhering to the RMII Specification Revision 1.2. RMII reduces the pin count of MII while retaining a serial management interface (MDIO/MDC) identical to MII. PLCA is fully supported through the RMII.

The RMII has the following characteristics:

- · A single 50 MHz clock reference is used for both transmit and receive

- · It provides independent 2-bit (di-bit) wide transmit and receive data paths

The RMII includes the following interface signals:

- Transmit Data TXD[1:0]

- Transmit Enable TXEN

- Receive Data RXD[1:0]

- Receive Error RXER

- Carrier Sense / Data Valid CRSDV

For timing information, refer to the RMII Timing section. Refer to the RMII Specification Revision 1.2 for additional information.

When operating in RMII mode, the LAN8670/1 REFCLKIN pin must be connected to a 50 MHz reference clock source. This clock source may be driven by the MAC or from a common oscillator driving both the MAC and LAN8670/1. When a common oscillator is utilized, it is recommended to match the length of the PCB traces from the source to the LAN8670/1 and MAC to within 0.5 inches (13 mm). Care should be taken when laying out the board to prevent the LAN8670/1 clock from becoming a victim of crosstalk as any noise introduced to the clock input of the LAN8670/1 could become radiated onto the network.

The CRSDV pin combines both carrier sense and receive data valid. On carrier sense, the CRSDV pin is asserted asynchronously to the 50 MHz reference clock. Thereafter, CRSDV is only negated synchronously to the reference clock. Carrier sense is indicated by the assertion of CRSDV during which the first di-bit of a data nibble is presented on RXD[1:0]. Similarly, receive data valid is indicated by the assertion of CRSDV when the second di-bit of a data nibble is presented on RXD[1:0]. See the RMII Specification Revision 1.2.

A collision is signaled on RMII by the assertion of carrier sense when the MAC is asserting TXEN. A half-duplex RMII MAC must be able to properly derive the collision indication from CRSDV and TXEN.

**Note:** The connection of a  $10 \text{ k}\Omega$  pull-down resistor on TXEN is recommended to prevent incidental transmission if the MAC does not actively pull-down or drive this pin low at all times during its reset and initialization.

#### **Related Links**

7.6.7 RMII Timing

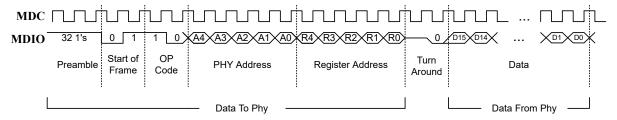

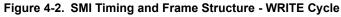

# 4.3 Serial Management Interface (SMI)

The Serial Management Interface (SMI) is used to control the device and obtain its status. This interface supports the standard PHY registers required by Clause 22 of IEEE Std 802.3, as well as "vendor-specific" registers allowed by the specification. Unimplemented registers will be read as hexadecimal "0000". Device registers are detailed in the Register Descriptions section.

At the system level, SMI provides two signals: MDIO and MDC. The MDC signal is an aperiodic clock provided by the station management entity (STA). MDIO is a bi-directional data SMI input/output signal that receives serial data (commands) from the STA and sends serial data (status) to the STA. The minimum time between edges of the MDC is 100 ns. There is no maximum time between edges. The minimum cycle time (i.e., the time between two consecutive rising or two consecutive falling edges) is 250 ns. These modest timing requirements allow this interface to be easily driven by the I/O port of a microcontroller.

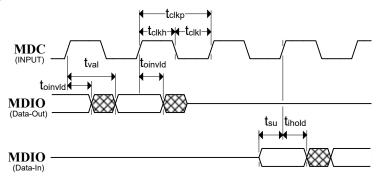

The data on the MDIO line is latched on the rising edge of the MDC. The management frame structure and timing is shown in the following figures. The timing relationships of the MDIO signals are further described in the SMI Timing section of the Operational Characteristics AC Specifications.

Figure 4-1. SMI Timing and Frame Structure - READ Cycle

#### **Related Links**

5. Register Descriptions7.6.8 SMI Timing

#### 4.3.1 Clause 45 Register Access

The LAN8670/1/2 only supports the MDIO management frame protocol defined in IEEE Std 802.3 Clause 22. Registers mapped into IEEE Std 802.3 Clause 45 MDIO Managed Devices (MMD) are accessed indirectly through the MMD Access Control (MMDCTRL) and MMD Access Address/Data (MMDAD) registers as described in IEEE Std 802.3 Annex 22D.

### **MMD Register Read**

The following process is used to indirectly read Clause 45 registers using the Clause 22 access mechanism.

- Write the MMD Access Control register with the MMD Function (FNCTN) field set to 00b and the Device Address (DEVID) field with the MDIO Management Device (MMD) address.

- 2. Write the address of the desired register to be read into the MMD Access Address/Data register.

- 3. Write the MMD Access Control register with the MMD Function field set to 01b, 10b, or 11b.

- Read the contents of the MMD's selected register from the MMD Access Address/Data register.

Subsequent reads from the MMD Access Address/Data register will continue to reread and return the value of the selected MMD register when the MMD Function field is set to 11b or 11b. When the MMD Function field is set to 10b, the MMD register address will be incremented following every read causing subsequent reads from the MMD Access Address/Data register to return data from the next higher MMD register.

#### **MMD Register Write**

The following process is used to indirectly write Clause 45 registers using the Clause 22 access mechanism.

- Write the MMD Access Control register with the MMD Function (FNCTN) field set to 00b and the Device Address (DEVID) field with the MDIO Management Device (MMD) address.

- 2. Write the address of the desired register to be written into the MMD Access Address/Data register.

- 3. Write the MMD Access Control register with the MMD Function field set to 01b, 10b, or 11b.

Subsequent writes to the MMD Access Address/Data register will continue to write to the selected MMD register when the MMD Function field is set to 10b or 11b, the MMD register address will be incremented following every write causing subsequent writes to the MMD Access Address/Data register to write data to the next higher MMD register.

#### **Related Links**

5.1.5 MMDCTRL5.1.6 MMDAD

# 4.4 Interrupt Management

The LAN8670/1/2 supports multiple interrupt capabilities which are not part of the IEEE 802.3 specification. An active low asynchronous interrupt signal may be generated on the IRQ\_N pin when selected status events are detected as configured by the Interrupt Mask Registers.

To assert an interrupt for a given event in the Status 1 (STS1) and Status 2 (STS2) registers, the corresponding mask bit in the Interrupt Mask 1 (IMASK1) and Interrupt Mask 2 (IMSK2) registers must be written to '0' to enable the interrupt. When the associated event occurs setting the status bit, the IRQ\_N pin will also be asserted. When the event to negate the status bit is true, or the corresponding bit in the Interrupt Mask Register is set disabling the interrupt, the IRQ\_N pin will be deasserted.

All interrupts are disabled (masked) following a reset with the exception of the Reset Complete interrupt mask bit. The Reset Complete interrupt mask is '0' by default such that the IRQ\_N pin will be asserted following a reset event setting the Reset Complete status bit. This may be used to alert the station management entity that the LAN8670/1/2 has been reset and is available for configuration.

#### **Related Links**

5.4.2 STS1

5.4.3 STS2

5.4.5 IMSK1

5.4.6 IMSK2

#### 4.5 Resets

The device provides the chip-level reset sources described in the following sections.

#### 4.5.1 Power-On Reset (POR)

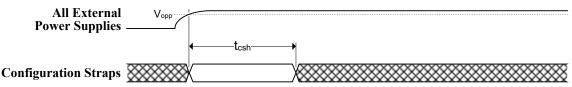

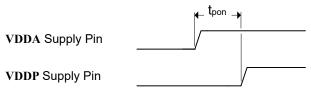

A Power-On Reset occurs whenever power is initially applied to the device, or if power is removed and reapplied to the device. A timer within the device will assert the internal reset for approximately 2 ms. Configuration straps are loaded by this reset and must adhere to the timing requirements specified in Power-On Configuration Strap Timing when not using the external pin reset (RESET N).

After power-on, the POR initially negates after the rising threshold is passed. In the event that the supply drops below the falling threshold, the POR asserts. The POR stays asserted until the rising threshold is once again crossed. The rising and falling thresholds are listed in Table 4-1.

Table 4-1. POR Supply Thresholds

| POR               | Rising Threshold <sup>1</sup> | Falling Threshold <sup>1</sup> |

|-------------------|-------------------------------|--------------------------------|

| VDDA              | 2.5V                          | 2.4V                           |

| 1.8V <sup>2</sup> | 1.6V                          | 1.3V                           |

#### Notes:

- 1. Rising and falling threshold voltages are design parameters and are neither tested nor characterized.

- 2. The internal 1.8V supply cannot be monitored externally.

### **Related Links**

7.6.3 Power-On Configuration Strap Timing

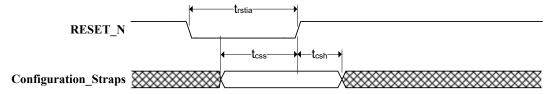

### 4.5.2 External Pin Reset (RESET\_N)

A hardware reset will occur when the RESET\_N pin is asserted. The RESET\_N pin must be connected externally to VDDP if unused. If used, the RESET\_N pin must be driven for a minimum period as defined in the RESET\_N Configuration Strap Timing section. Configuration straps are loaded by the reset.

#### **Related Links**

7.6.4 RESET N Configuration Strap Timing

#### 4.5.3 Software Reset

The software reset is available via the PHY Soft Reset (SW RESET) bit in the Basic Control register.

Configuration straps are not loaded by a software reset.

#### **Related Links**

5.1.1 BASIC CONTROL

### 4.6 Power Management

A summary of the device's available power states is provided in the table below.

Table 4-2. Power Management States

| State  | Description                                                  |

|--------|--------------------------------------------------------------|

| RESET  | The device is in this state when the RESET_N pin is asserted |

| ACTIVE | The device is fully active                                   |

### 4.7 Initialization

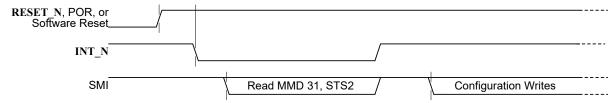

When the device is in a reset state, the IRQ\_N interrupt pin is high-impedance and will be pulled high through an external pull-up resistor. Once all device reset sources are deasserted, the device will begin its internal initialization. The device will assert the Reset Complete (RESETC) bit in the Status 2 (STS2) register to indicate that it has completed its internal initialization and is ready for configuration. As the Reset Complete status is non-maskable, the IRQ\_N pin will always be asserted and driven low following a device reset.

At the system level, the station management entity should respond to all assertions of the IRQ\_N pin with a read of critical status registers through the Serial Management Interface (SMI), including the Status 2 register. Upon reading of the Status 2 register, the pending Reset Complete status bit will be automatically cleared causing the IRQ\_N pin to be released and pulled high again. The station management entity may then continue to configure the device registers through the Serial Management Interface. See Figure 4-3 for an illustration of the device reset, initialization, and configuration process.

Figure 4-3. Initialization and Configuration Sequence

#### **Related Links**

5.4.3 STS2

4.5 Resets

# 4.8 Clock Manager

The Clock Manager generates the internal clocks from an external reference source.

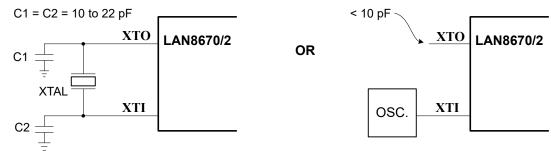

## 4.8.1 Crystal Pins (XTI/XTO)

The XTI and XTO crystal oscillator pins are used to connect a 25.0 MHz clock source for MII operation. The crystal oscillator should be in a fundamental, parallel resonant mode. Figure 4-4 depicts the external circuitry connected to the LAN8670/1/2 oscillator circuit. Since the internal inverter/amplifier is operated in its linear region, external series resistors should not be used as they will lower the gain and could cause start-up problems. Several factors must be considered when selecting a crystal including load capacitance, oscillator margin, cut, and operating temperature. The crystal frequency must be 25.0 MHz.

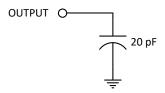

If an external clock oscillator is used in lieu of a crystal oscillator, it must be connected to the XTI pin. The clock must be stable prior to the negation of reset and remain stable for proper operation. In addition, the XTO pin should float and have minimal capacitance (see Figure 4-4).

Figure 4-4. Crystal Oscillator Input

#### **Related Links**

6.4 Crystal Oscillator Selection

7.8.1 Crystal Specifications

### 4.8.2 Reference Clock (REFCLKIN)

The REFCLKIN pin is used to connect an external 50.0 MHz reference clock source for RMII operation. The clock source must be stable prior to the negation of reset and remain stable for proper operation. In addition, the LAN8670 XTO pin should float and have minimal capacitance (<10 pF).

Reference clock requirements are found in the RMII REFCLKIN Requirements section.

#### **Related Links**

7.8.2 RMII REFCLKIN Requirements

# 4.9 Physical Layer Collision Avoidance (PLCA)

PLCA operates in conjunction with a CSMA/CD MAC to actively avoid collisions among half-duplex stations (known as PLCA *nodes*) allowing for greater network utilization. Each node on the network segment (i.e., collision domain) is assigned a unique *Local ID*. *Transmit opportunities* are then granted to each node in sequence based on their Local ID. The node configured as Local ID = 0 is known as the *PLCA coordinator*. The role of the PLCA coordinator is to transmit a periodic synchronizing BEACON onto the physical media. All other nodes are referred to as a *PLCA follower* as they follow the synchronization of the coordinator. Once the BEACON has been received on the segment, all nodes begin counting transmit opportunities beginning with zero. Nodes detect their assigned transmit opportunity by counting the number of opportunities that have passed since the transmission of the BEACON by the PLCA coordinator. Each node may transmit when the number of transmit opportunities counted since the BEACON matches the Local ID assigned to the node. Within each transmit opportunity, the node assigned the current opportunity may either transmit a packet or yield. Once the node has transmitted a packet (or yielded), each node increments the transmit opportunity counter and the transmit opportunity goes to the next node. The first transmit opportunity of zero allows node with Local ID = 0 to transmit. Once a fixed number of transmit opportunities has been provided, the PLCA coordinator will transmit another BEACON starting the cycle over again. A BEACON followed by a fixed number of transmit opportunities is known as a *PLCA bus cycle*.

On multidrop topologies with multiple nodes connected to a shared media mixing segment, PLCA enables a fairness in opportunity to transmit such that one node cannot transmit more than one frame without each of the other nodes also being granted an opportunity to transmit. An exception to this is that PLCA also allows individual nodes, if desired within the engineered network segment, to be configured to transmit a burst of frames within a single transmit opportunity.

PLCA is enabled by setting the PLCA Enable bit in the PLCA Control 0 (PLCA\_CTRL0) register. The node Local ID is configured within the PLCA Local ID (ID) field of the PLCA Control 1 (PLCA\_CTRL1) register and must be unique within the PLCA network segment to successfully avoid collisions. Additionally, the Local ID must be less than the number of transmit opportunities in each bus cycle in order to be granted a transmit opportunity (see the Node Count field of the PLCA Control 1 register). When the node is configured as the PLCA coordinator, then the number of transmit opportunities within each PLCA bus cycle (period between successive BEACON transmissions) is configured in the Node Count (NCNT) field of the PLCA Control 1 register.

The time for each transmit opportunity is configured within the PLCA Transmit Opportunity Timer (PLCA\_TOTMR) register. The transmit opportunity timer must be set equal among all nodes in the PLCA collision domain to maintain

# **Functional Descriptions**

synchronization among the nodes. The default transmit opportunity timer value is appropriate for segments specified in IEEE 802.3 Clause 147 and should only be changed in special circumstances.

When PLCA has been enabled on a node, the PLCA Status bit in the PLCA Status (PLCA\_STS) register will indicate if the node is actively receiving a periodic PLCA BEACON. This may be useful for diagnosing a misbehaving PLCA network segment.

#### **Related Links**

4.9.1 PLCA Burst Mode5.4.14 PLCA\_CTRL05.4.15 PLCA\_CTRL15.4.17 PLCA\_TOTMR5.4.16 PLCA STS

### 4.9.1 PLCA Burst Mode

Some applications, such as sensors or audio, may require the transmission of frequent small frames with a limited latency. As PLCA enables only one transmit opportunity for each node in each bus cycle, these applications may experience significant latency when they are connected onto a multidrop mixing segment with applications that transmit large packets. For example, an audio application may require the transmission of eight stereo 16-bit audio samples as 64 byte packets every 167 µs with minimal latency. When another node on the segment transmits a 1500 byte packet it will occupy the channel for 1.2 ms. The audio application will therefore buffer seven audio packets during the time that the channel is occupied. With standard PLCA, the audio application will only be able to transmit one of its audio packets during the next PLCA bus cycle. The result is that each successive audio packet the audio application needs to transmit is delayed with increasing latency.

One solution to this problem is to allow specific nodes to transmit more than one packet during its transmit opportunity. This ability to transmit a burst of multiple packet allows the audio application in the above example to empty its buffers and transmit all audio packets that it has queued, preventing the latency of the audio packets to grow beyond a tolerable limit.

The ability to transmit packets in a burst is configurable individually for each node on the segment. The Maximum Burst Count (MAXBC) field in the PLCA Burst Mode (PLCA\_BURST) register configures the maximum number of additional packets allowed to transmit in each of the node's transmit opportunities. This is in addition to the initial packet that may be transmitted by the node in its transmit opportunity. Additionally, the Burst Timer (BTMR) field configures the amount of time the node may transmit (COMMIT) to maintain a hold on its current transmit opportunity after transmitting a packet to allow the MAC to transmit an additional packet. Once this timer expires, the node will then yield the transmit opportunity to the next node.

#### **Related Links**

5.4.18 PLCA\_BURST

#### 4.9.2 Physical Layer Collision Avoidance (PLCA) Diagnostics

The LAN8670/1/2 PHY implements a number of features useful to the detection of PLCA misconfiguration on the network segment. These features include error status indications and event counters.

The PLCA error status indicators are located in the Status 1 (STS1) register. Each indication also has an associated interrupt mask bit in the Interrupt Mask 1 (IMSK1) register to enable an assertion on the IRQ\_N interrupt pin when the event is detected.

Each node of a PLCA segment must be assigned a unique node ID to properly avoid collisions. The device has the ability to detect that another node is assigned the same Local ID by detecting the reception of a packet from the network during its assigned transmit opportunity. When this condition occurs, the Receive in Transmit Opportunity (RXINTO) status bit is set. Additionally, should a collision be detected while the device is transmitting in its assigned transmit opportunity, the Transmit Collision (TXCOL) status bit will be set.

Multiple nodes configured and acting as PLCA Coordinators also cause problems. Multiple Coordinators on the mixing segment will each transmit a BEACON according to its own PLCA bus cycle and timing. The result is that each Coordinator will receive BEACONs that it did not transmit. When configured as a PLCA Coordinator, it will set the Unexpected BEACON Received (UNEXPB) status bit to indicate the presence of another Coordinator on the network segment.

# **Functional Descriptions**

The PLCA Coordinator must be configured with the correct number of nodes on the segment to permit the proper number of transmit opportunities per bus cycle. If the Coordinator is configured to allow for too few transmit opportunities between BEACONs, Follower nodes may not receive their assigned transmit opportunity. When the device is operating as a PLCA Follower, if it detects a BEACON before its assigned transmit opportunity occurs then the BEACON Received Before Transmit Opportunity (BCNBFTO) status bit is set to indicate that the configured PLCA bus cycle is too small to allow the Follower to transmit.

When configured as a PLCA Follower, the PLCA Status (PST) bit in the PLCA Status (PLCA\_STS) register will be set as long as BEACONs are regularly being received from a Coordinator. If BEACONs are not received by the device it will continue incrementing its transmit opportunity counter. When the transmit opportunity counter reaches the maximum count of 255, it will then stop incrementing and a 13 ms timer started. If no BEACON is received after the timer expires, the PLCA Status bit will be cleared. When the PLCA Status bit is zero, the device will revert to CSMA/CD operation with PLCA deactivated. Once a BEACON is received the device will set the PLCA Status bit and return to normal PLCA operation. Refer to Clause 148 of the IEEE 802.3cg specification for additional details.

**Note:** The PLCA Status (PST) bit cannot generate an interrupt assertion on the IRQ\_N pin and must therefore be polled by reading the PLCA Status (PLCA STS) register.

Two event counters are implemented to aid the station controller in monitoring PLCA on the segment. These counters include a transmit opportunity counter and a BEACON counter. Each counter is enabled by setting the corresponding enable bit in the Counter Control (CTRCTRL) register. Writing a '1' to the Transmit Opportunity Counter Enable (TOCTRE) bit enables the transmit opportunity counter. The BEACON Counter Enable (BCNCTRE) bit enables the BEACON counter when set.

When enabled, the Transmit Opportunity Count High/Low (TOCNTH/TOCNTL) registers will contain the number of transmit opportunities the local PHY could have used to transmit since the last read. By polling the counter, the station controller can monitor that PLCA is active and that the PHY can transmit packets when needed.

Similarly, the BEACON Count High/Low (BCNCNTH/BCNCNTL) register contains the number of received BEACONs since the last read. The station controller can poll this counter to monitor the health of the PLCA Coordinator.

#### **Related Links**

5.4.2 STS1

5.4.5 IMSK1

5.4.16 PLCA\_STS

5.4.7 CTRCTRL

**5.4.8 TOCNTH**

**5.4.9 TOCNTL**

**5.4.10 BCNCNTH**

**5.4.11 BCNCNTL**

#### 5. **Register Descriptions**

This chapter describes the various device registers, which are categorized as follows:

- SMI Basic Control and Status Registers (Clause 22)

- PMA/PMD Registers (MMD 1)

- PCS Registers (MMD 3)

- Miscellaneous Registers (MMD 31)

For details on register bit attribute notation, refer to the section Register Bit Types.

### **Related Links**

1.3 Register Bit Types

# 5.1 SMI Basic Control and Status Registers

The section describes the various SMI Control and Status Registers (CSRs). The SMI CSRs follow the IEEE 802.3 (Clause 22.2.4) management register set. All functionality and bit definitions comply with these standards.

**MARNING**

RESERVED address space must not be written under any circumstances. Failure to heed this warning may result in adverse operation and unexpected results.

| Address          | Name          | Bit Pos. | 7             | 6                         | 5                         | 4                       | 3                       | 2                         | 1                         | 0                  |

|------------------|---------------|----------|---------------|---------------------------|---------------------------|-------------------------|-------------------------|---------------------------|---------------------------|--------------------|

| 0x00             | BASIC_CONTROL | 15:8     | SW_RESET      | LOOPBACK                  | SPD_SEL[0]                | AUTO_NEG_<br>EN         | PD                      | ISOLATE                   | RE_AUTO_N<br>EG           | DUPLEX_MO<br>DE    |

|                  |               | 7:0      | COL_TEST      | SPD_SEL[1]                |                           |                         |                         |                           |                           |                    |

|                  |               | 15:8     | 100BASE-T4    | 100BASE-TX<br>Full Duplex | 100BASE-TX<br>Half Duplex | 10BASE-T<br>Full Duplex | 10BASE-T<br>Half Duplex | 100BASE-T2<br>Full Duplex | 100BASE-T2<br>Half Duplex | Extended<br>Status |

| 0x01             | BASIC_STATUS  | 7:0      |               | MF_PRE_SU<br>P            | AUTO_NEG_<br>COMP         | RMT_FAULT               | AUTO_NEG                | LINK_STAT                 | JAB_DET                   | EXT_CAP            |

| 0x02             | PHY ID0       | 15:8     |               |                           | ,                         | OUI                     | [2:9]                   |                           |                           |                    |

| 0x02             | PHT_ID0       | 7:0      |               |                           |                           | OUI[1                   | 0:17]                   |                           |                           |                    |

| 0x03             | PHY ID1       | 15:8     |               |                           | OUI[1                     | 8:23]                   |                         |                           | MODE                      | EL[5:4]            |

| 0.000            | FIII_IDI      | 7:0      |               | MODE                      | EL[3:0]                   |                         | REV[3:0]                |                           |                           |                    |

| 0x05<br><br>0x0C | Reserved      |          |               |                           |                           |                         |                         |                           |                           |                    |

| 0x0D             | MMDCTDI       | 15:8     | FNCT          | N[1:0]                    |                           |                         |                         |                           |                           |                    |

| UXUD             | MMDCTRL       | 7:0      |               |                           |                           |                         |                         | DEVAD[4:0]                |                           |                    |

| 0x0E             | MMDAD         | 15:8     |               |                           |                           | ADR_DA                  | TA[15:8]                |                           |                           |                    |

| UXUL             | IVIIVIDAD     | 7:0      | ADR_DATA[7:0] |                           |                           |                         |                         |                           |                           |                    |

| 0x10             |               |          |               |                           |                           |                         |                         |                           |                           |                    |

| <br>0x11         | Reserved      |          |               |                           |                           |                         |                         |                           |                           |                    |