#### **MAX14646E**

## **USB Charger Detection** with Integrated Overvoltage Protector

#### **General Description**

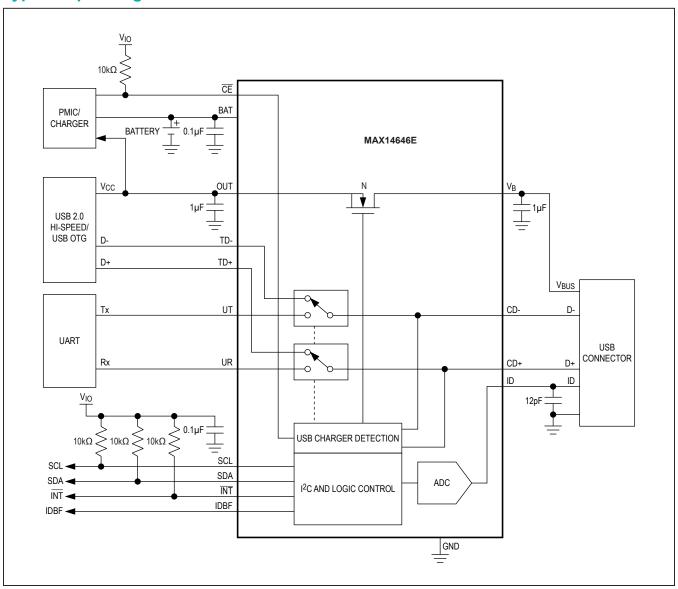

The MAX14646E is a USB charger detector which includes advanced features from USB Battery Charging Specification Revision 1.2. The USB charger detection circuitry detects USB standard downstream ports (SDPs), USB charging downstream ports (CDPs), or dedicated charger ports (DCPs), and controls an external lithium-ion (Li+) battery charger.

The device implements USB Battery Charging Specification detection logic. It also includes Apple® charger detection that allows identification of resistor divider networks on D+/D-.

The internal double-pole double-throw (DPDT) USB switch is compliant to Hi-Speed USB, full-speed USB, low-speed USB, and UART signals. The device's internal switch features low on-resistance, low on-resistance flatness, and very low capacitance. The ID pin controls the DPDT switch position. The MAX14646E features high-ESD protection up to ±15kV Human Body Model (HBM) on the CD+, CD-, and ID pins.

The IC is available in a 16-bump, 0.4mm pitch, 1.8mm x 1.9mm WLP package and operates over the -40°C to +85°C extended temperature range.

#### **Applications**

- DSCs and Camcorders

- Tablet PCs

- Smartphones

- e-Readers

#### **Benefits and Features**

- Consumes Less Power

- Low Battery Standby Current 5μA (typ)

- Delivers USB Compliance and Flexibility

- Includes Advanced Features from USB Battery Charging Specification Revision 1.2

- Data Contact Detection for Foolproof Connector Insertion Detection

- · Dedicated Charger Detection

- · Standard Downstream Port Detection

- · Charging Downstream Port Detection

- · Apple Charger Detection

- Sony<sup>®</sup> Charger Detection\*

- Facilitates System Design

- Integrated Precision 1.5A Overvoltage Protection (OVP)

- Negative Audio Capable DPDT Hi-Speed USB Switches

- · Automatic Switch and Charger Interface Control

- Full Control by I2C Interface

- · Interrupt for Device Status Change

- Saves Board Space

- V<sub>BUS</sub> Connection Capable of 36V

- ±15kV HBM ESD Protection

- 1.8mm x 1.9mm WLP Package

Ordering Information appears at end of data sheet.

Typical Operating Circuit appears at end of data sheet.

\*Contact factory for the list of compatible chargers.

Apple is a registered tradema`rk of Apple, Inc.

Sony is a registered trademark and registered service mark of Kabushiki Kaisha TA Sony Corporation.

### **Absolute Maximum Ratings**

| (Voltages referenced to GND.)                                 |

|---------------------------------------------------------------|

| BAT, INT, SDA, SCL, CE, ID, IDBF0.3V to +6.0V                 |

| OUT0.3V to Minimum (V <sub>B</sub> + 0.3V, +6.0V)             |

| V <sub>B</sub> 0.3V to +40V                                   |

| CP_EN = 1 (Note 1)                                            |

| CD+, CD-, UT, UR2.1V to (V <sub>SWPOS</sub> + 0.3V)           |

| TD+, TD0.3V to (V <sub>SWPOS</sub> + 0.3V)                    |

| CP_EN = 0 (Note 2)                                            |

| CD+, CD-, TD+, TD-, UT, UR0.3V to (V <sub>CCINT</sub> + 0.3V) |

| Continuous Current into Any Other Terminal $\pm 50$ mA Continuous Power Dissipation ( $T_A = +70^{\circ}$ C) WLP (derate 17.2mW/°C above $+70^{\circ}$ C) | Continuous Current into V <sub>B</sub> , OUT          | ±1.5A          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------|

| WLP (derate 17.2mW/°C above +70°C)                                                                                                                        | Continuous Current into Any Other Terminal            | ±50mA          |

| Operating Temperature Range -40°C to +85°C  Junction Temperature +150°C  Storage Temperature Range -65°C to +150°C                                        | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| Junction Temperature                                                                                                                                      | WLP (derate 17.2mW/°C above +70°C)                    | 1376mW         |

| Storage Temperature Range65°C to +150°C                                                                                                                   | Operating Temperature Range                           | 40°C to +85°C  |

| 0 1                                                                                                                                                       | Junction Temperature                                  | +150°C         |

| Soldering Temperature (reflow) +260°C                                                                                                                     | Storage Temperature Range                             | 65°C to +150°C |

| Coldering Temperature (Tellow)                                                                                                                            | Soldering Temperature (reflow)                        | +260°C         |

Note 1:  $V_{SWPOS} = min (V_{CCINT} or 3.3V)$ .

**Note 2:**  $V_{CCINT} = max (V_{BAT} \text{ or min } (V_B \text{ or } 3.7V)).$

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 3)**

**WLP**

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) .........58°C/W

Note 3: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{BAT}$  = +2.8V to +5.5V,  $V_{B}$  = +3.5V to +36V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = +3.6V,  $V_{B}$  = +5.0V,  $T_{A}$  = +25°C.) (Note 4)

| PARAMETER                          | SYMBOL             | CONDITIONS                                                                                                                          | MIN   | TYP   | MAX   | UNITS |

|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| DC CHARACTERISTICS                 |                    |                                                                                                                                     |       |       |       |       |

| Supply Voltage Dange               | V <sub>BAT</sub>   |                                                                                                                                     | 2.8   |       | 5.5   | V     |

| Supply Voltage Range               | V <sub>B</sub>     |                                                                                                                                     | 3.5   |       | 36    | ]     |

| Internal Positive Switch Regulator | V <sub>SWPOS</sub> |                                                                                                                                     | 3.3   | 3.4   | 3.5   | V     |

| Internal Negative Switch Regulator | V <sub>SWNEG</sub> |                                                                                                                                     | -2.08 | -1.97 | -1.8  | V     |

|                                    | \/                 | Rising edge                                                                                                                         | 0.5   | 1.6   | 2.6   | V     |

| POR                                | VCCINT             | Falling edge                                                                                                                        |       |       | 2.35  | 7     |

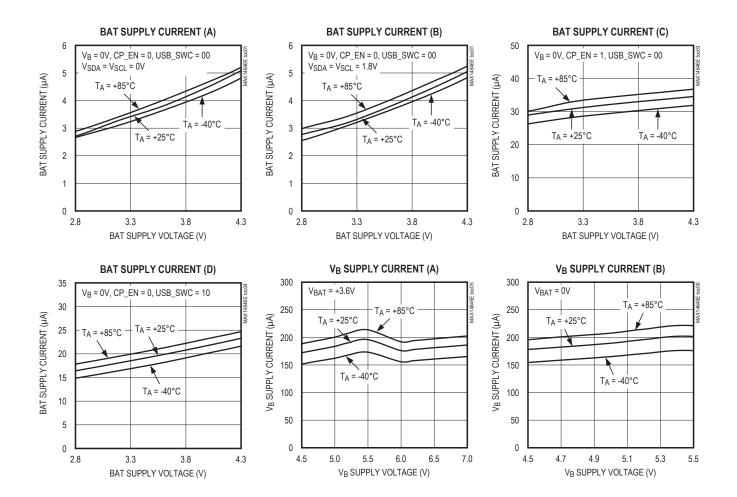

| BAT Supply Current                 | 1                  | V <sub>BAT</sub> = 4.2V, V <sub>B</sub> = 0V, CP_EN = 0,<br>USB_SWC = 00, ADC_EN = 0,<br>V <sub>SDA</sub> = V <sub>SCL</sub> = 0.4V |       | 5     | 7.5   | μA    |

|                                    | BAT                | V <sub>BAT</sub> = 4.2V, V <sub>B</sub> = 0V, CP_EN = 1,<br>USB_SWC = 11, ADC_EN = 1,<br>V <sub>SDA</sub> = V <sub>SCL</sub> = 1.8V |       | 49    | 49 80 |       |

| V <sub>B</sub> Supply Current      | I <sub>VB</sub>    | V <sub>B</sub> = 5.5V, CP_EN = 1,<br>USB_SWC = 00                                                                                   |       | 200   | 360   | μA    |

( $V_{BAT}$  = +2.8V to +5.5V,  $V_{B}$  = +3.5V to +36V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = +3.6V,  $V_{B}$  = +5.0V,  $T_{A}$  = +25°C.) (Note 4)

| PARAMETER                                                   | SYMBOL                                         | CON                                                                                 | MIN                                                    | TYP                | MAX  | UNITS              |    |

|-------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------|------|--------------------|----|

| OVERVOLTAGE PROTECTION                                      |                                                |                                                                                     |                                                        |                    |      |                    |    |

| Switch On-Resistance                                        | R <sub>ON</sub>                                | $V_B = 5V, I_{OUT} = -80$                                                           |                                                        | 60                 | 130  | mΩ                 |    |

| Overvoltage Lockout Cutoff Threshold                        | V <sub>OVLO</sub>                              | Rising edge of V <sub>B</sub>                                                       | Rising edge of V <sub>B</sub>                          |                    |      | 6.0                | V  |

| Overvoltage Lockout<br>Hysteresis                           |                                                | Falling edge of V <sub>B</sub>                                                      |                                                        | 5.50               |      |                    | V  |

| OUT Load Capacitance                                        |                                                | I <sub>OUT</sub> up to 1.5A                                                         |                                                        | 1                  |      |                    | μF |

| Thermal Shutdown Threshold                                  |                                                |                                                                                     |                                                        |                    | +150 |                    | °C |

| Thermal Shutdown Hysteresis                                 |                                                |                                                                                     |                                                        |                    | 20   |                    | °C |

| CHARGER DETECTION                                           |                                                |                                                                                     |                                                        |                    |      |                    |    |

| V <sub>DAT_SRC</sub> Voltage                                | V <sub>DP_SRC</sub>                            | With I <sub>DP_SRC</sub> = 0 to                                                     | ο 200μΑ                                                | 0.5                |      | 0.7                | V  |

| V <sub>DAT_REF</sub> Voltage                                | V <sub>DAT_REF</sub>                           |                                                                                     |                                                        | 0.25               |      | 0.4                | V  |

| V <sub>LGC</sub> Voltage                                    | V <sub>LGC</sub>                               |                                                                                     |                                                        | 1                  |      | 1.5                | V  |

| I <sub>DP_SRC</sub> Current                                 | I <sub>DP_SRC</sub>                            | 0 to 2.5V                                                                           |                                                        | 6                  |      | 11                 | μA |

| R <sub>DM</sub> Pulldown Resistor                           | R <sub>DM_DWN</sub>                            |                                                                                     |                                                        | 14.25              |      | 24.8               | kΩ |

| CD+ and CD- Sink Current                                    | I <sub>CD+_SINK</sub> ,<br>I <sub>CDSINK</sub> | 150mV to 3.6V                                                                       |                                                        | 50                 |      | 150                | μА |

| Charger Detection Weak Sink                                 | I <sub>WEAK</sub>                              | V <sub>CD-</sub> = 3.6V                                                             |                                                        |                    |      | 0.3                | μA |

| V <sub>BUS25</sub> Ratio                                    | V <sub>BUS25</sub>                             | Reference ratio for percentage of V <sub>BUS</sub>                                  | special charger as a<br>S voltage, V <sub>B</sub> = 5V | 22.5               | 25   | 27.5               | %  |

| V <sub>BUS47</sub> Ratio                                    | V <sub>BUS47</sub>                             | Reference ratio for percentage of V <sub>BUS</sub>                                  | special charger as a<br>S voltage, V <sub>B</sub> = 5V | 42.3               | 47   | 51.7               | %  |

| V <sub>BUS60</sub> Ratio                                    | V <sub>BUS60</sub>                             | Reference ratio for percentage of V <sub>BUS</sub>                                  | special charger as a<br>S voltage, V <sub>B</sub> = 5V | 57                 | 60   | 63                 | %  |

| Ohannan Datast Carras Times                                 | 1                                              | DCHK_TM = 0                                                                         |                                                        | 40                 |      |                    |    |

| Charger Detect Source Time                                  | tDP_SRC_ON                                     | DCHK_TM = 1                                                                         |                                                        |                    | 625  |                    | ms |

| Charger Detect Type<br>Detection Time                       | tDP_RES_ON                                     | From V <sub>B</sub> > V <sub>VBDET</sub>                                            | to detection                                           | 120                |      |                    | ms |

| Charger Detect Delay Time                                   | tDP_SRC_HICRNT                                 |                                                                                     |                                                        | 40                 |      | 80                 | ms |

| V Attack to OF Outside Time                                 |                                                | From V <sub>B</sub> > V <sub>VBDET</sub> to CE change, DCF                          | or CHG_TYP_M = 1<br>HK_TM = 0                          |                    |      | 520                |    |

| V <sub>B</sub> Attach to $\overline{\text{CE}}$ Output Time | tvbsw                                          | From V <sub>B</sub> > V <sub>VBDET</sub> or CHG_TYP_M = 1 to CE change, DCHK_TM = 1 |                                                        |                    |      | 1450               | ms |

| V <sub>B</sub> Detect Threshold                             | V <sub>VBDET</sub>                             | Rising edge                                                                         |                                                        | 3.3                | 3.4  | 3.5                | V  |

| V <sub>B</sub> Detect Hysteresis                            | V <sub>VBDET_HYS</sub>                         |                                                                                     |                                                        |                    | 400  |                    | mV |

| USB ANALOG SWITCHES (CD                                     |                                                |                                                                                     |                                                        |                    |      |                    |    |

|                                                             |                                                | CP_EN = 0                                                                           |                                                        | 0                  |      | $V_{CCINT}$        |    |

| Analog Signal Range                                         | V <sub>CD+</sub> , V <sub>CD-</sub>            | CP EN = 1                                                                           | TD+, TD-                                               | 0                  |      | V <sub>SWPOS</sub> | V  |

|                                                             |                                                | OL.\ - 1                                                                            | UR, UT                                                 | V <sub>SWNEG</sub> |      | $V_{SWPOS}$        |    |

( $V_{BAT}$  = +2.8V to +5.5V,  $V_{B}$  = +3.5V to +36V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = +3.6V,  $V_{B}$  = +5.0V,  $T_{A}$  = +25°C.) (Note 4)

| PARAMETER                            | SYMBOL                     | CONDITIONS                                                 |                                                                                                                       | MIN  | TYP   | MAX  | UNITS |  |

|--------------------------------------|----------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|--|

| On-Resistance                        | R <sub>ONUSB</sub>         |                                                            | $V_{BAT} = 3.0V$ , $I_{CD+}$ or $I_{CD-} = 10$ mA, $V_{CD+}$ or $V_{CD-} = 0$ to $3.0V$                               |      |       | 6    | Ω     |  |

| On-Resistance Match Between Channels | $\Delta R_{	extsf{ONUSB}}$ |                                                            | V <sub>BAT</sub> = 3.0V, I <sub>CD+</sub> or I <sub>CD-</sub> = 10mA,<br>V <sub>CD+</sub> or V <sub>CD-</sub> = 400mV |      |       | 0.5  | Ω     |  |

| On-Resistance Flatness               | R <sub>FLATUSB</sub>       | $V_{BAT}$ = 3.0V, $I_{C}$<br>$V_{CD+}$ or $V_{CD-}$ =      | D+ or I <sub>CD</sub> - = 10mA,<br>0 to 3.3V                                                                          |      | 0.06  | 0.2  | Ω     |  |

| Off-Leakage Current                  | I <sub>LUSB(OFF)</sub>     |                                                            | vitch open; V <sub>UT</sub> , V <sub>UR</sub> ,<br>= 0.3V, 2.5V; V <sub>CD+</sub> or<br>3V                            | -360 |       | +360 | nA    |  |

| On-Leakage Current                   | I <sub>LUSB(ON)</sub>      | V <sub>BAT</sub> = 4.2V, sv<br>V <sub>CD+</sub> = 0.3V, 2. | vitch closed; V <sub>CD-</sub> or<br>5V                                                                               | -360 |       | +360 | nA    |  |

| ANALOG INPUT (ID) (Note 5)           |                            |                                                            |                                                                                                                       |      |       |      |       |  |

|                                      |                            | 00000                                                      | GND                                                                                                                   |      |       | 1.5  |       |  |

|                                      |                            | 00001                                                      | R1                                                                                                                    |      | 2.21  |      |       |  |

|                                      |                            | 00010                                                      | R2                                                                                                                    |      | 2.8   |      |       |  |

|                                      |                            | 00011                                                      | R3                                                                                                                    |      | 3.48  |      |       |  |

|                                      |                            | 00100                                                      | R4                                                                                                                    |      | 4.22  |      |       |  |

|                                      |                            | 00101                                                      | R5                                                                                                                    |      | 5.11  |      |       |  |

|                                      |                            | 00110                                                      | R6                                                                                                                    |      | 6.04  |      | ]     |  |

|                                      |                            | 00111                                                      | R7                                                                                                                    |      | 7.87  |      |       |  |

|                                      |                            | 01000                                                      | R8                                                                                                                    |      | 10.02 |      |       |  |

|                                      |                            | 01001                                                      | R9                                                                                                                    |      | 12.1  |      |       |  |

|                                      |                            | 01010                                                      | R10                                                                                                                   |      | 14.7  |      |       |  |

|                                      |                            | 01011                                                      | R11                                                                                                                   |      | 17.8  |      |       |  |

|                                      |                            | 01100                                                      | R12                                                                                                                   |      | 21.5  |      |       |  |

|                                      |                            | 01101                                                      | R13                                                                                                                   |      | 25.5  |      |       |  |

| ADC Detection Resistors              |                            | 01110                                                      | R14                                                                                                                   |      | 30.1  |      |       |  |

| (Use ±1% Resistors for R1 to         | R <sub>ADC</sub>           | 01111                                                      | R15                                                                                                                   |      | 36.5  |      | kΩ    |  |

| R30)                                 | MADC                       | 10000                                                      | R16                                                                                                                   |      | 45.3  |      | 1132  |  |

|                                      |                            | 10001                                                      | R17                                                                                                                   |      | 53.6  |      |       |  |

|                                      |                            | 10010                                                      | R18                                                                                                                   |      | 64.9  |      |       |  |

|                                      |                            | 10011                                                      | R19                                                                                                                   |      | 80.06 |      |       |  |

|                                      |                            | 10100                                                      | R20                                                                                                                   |      | 102   |      |       |  |

|                                      |                            | 10101                                                      | R21                                                                                                                   |      | 121   |      |       |  |

|                                      |                            | 10110                                                      | R22                                                                                                                   |      | 150   |      | _     |  |

|                                      |                            | 10111                                                      | R23                                                                                                                   | 175  | 200   | 202  |       |  |

|                                      |                            | 11000                                                      | R24                                                                                                                   |      | 232   |      | _     |  |

|                                      |                            | 11001                                                      | R25                                                                                                                   |      | 267   |      | _     |  |

|                                      |                            | 11010                                                      | R26                                                                                                                   |      | 309   |      | _     |  |

|                                      |                            | 11011                                                      | R27                                                                                                                   |      | 365   |      | _     |  |

|                                      |                            | 11100                                                      | R28                                                                                                                   |      | 422   |      | _     |  |

|                                      |                            | 11101                                                      | R29                                                                                                                   |      | 491   |      |       |  |

|                                      |                            | 11110                                                      | R30                                                                                                                   |      | 576   |      | _     |  |

|                                      |                            | 11111                                                      | Open                                                                                                                  | 750  |       |      |       |  |

( $V_{BAT}$  = +2.8V to +5.5V,  $V_{B}$  = +3.5V to +36V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = +3.6V,  $V_{B}$  = +5.0V,  $T_{A}$  = +25°C.) (Note 4)

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                                                                             | MIN                    | TYP  | MAX | UNITS |

|-------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|-------|

| DIGITAL SIGNALS (INT, CE, SC                    | CL, SDA)             |                                                                                                                        |                        |      |     | •     |

| Input Logic-High                                | V <sub>IH</sub>      |                                                                                                                        | 1.4                    |      |     | V     |

| Input Logic-Low                                 | V <sub>IL</sub>      |                                                                                                                        |                        |      | 0.4 | V     |

| Input Leakage Current                           | INLEAK               |                                                                                                                        | -1                     |      | +1  | μA    |

| Output Leakage Current                          | I <sub>LEAK</sub>    | V <sub>IO</sub> = 3.3V                                                                                                 |                        |      | 1   | μA    |

| Output Logic-Low Voltage (INT, CE)              | V <sub>OL</sub>      | I <sub>SINK</sub> = 1mA                                                                                                |                        |      | 0.2 | V     |

| DIGITAL OUTPUT (IDBF)                           |                      |                                                                                                                        |                        |      |     |       |

| Output Logic-High                               |                      | V <sub>OUT</sub> = 5.5V, I <sub>SOURCE</sub> = 1mA                                                                     | V <sub>OUT</sub> - 0.4 |      | 1   | V     |

| Output Logic-Low                                | V <sub>OL</sub>      | I <sub>SINK</sub> = 1mA                                                                                                |                        |      | 0.4 | V     |

| Output Logic High Impedance                     | I <sub>LEAK</sub>    |                                                                                                                        | -1                     |      | +1  | μA    |

| DYNAMIC PERFORMANCE                             |                      |                                                                                                                        |                        |      |     | •     |

| Analog-Switch Turn-On Time                      | t <sub>ON</sub>      | $I^2$ C stop to switch on, $R_L$ = 50Ω                                                                                 |                        | 0.02 | 1   | ms    |

| Analog-Switch Turn-Off Time                     | t <sub>OFF</sub>     | $I^2$ C stop to switch off, $R_L = 50Ω$                                                                                |                        | 0.02 | 0.1 | ms    |

| Debounce Time                                   | t <sub>MDEB</sub>    | Main debounce, all comparators                                                                                         | 20                     | 30   | 40  | ms    |

| Off-Capacitance                                 | C <sub>OFF</sub>     | TD-, TD+ applied voltage is 0.5V <sub>P-P</sub> , DC bias = 0V, f = 240MHz                                             |                        | 2    |     | pF    |

| On-Capacitance                                  | C <sub>ON</sub>      | TD-, TD+ applied voltage is 0.5V <sub>P-P</sub> , DC bias = 0V, f = 240MHz, CD- connected to TD-, CD+ connected to TD+ |                        | 7    |     | pF    |

| -3dB Bandwidth                                  | BW                   |                                                                                                                        |                        | 1    |     | GHz   |

| Crosstalk                                       |                      | $R_L = 50\Omega$ , $f = 20kHz$ , $V_{CD} = 0.5V_{P-P}$                                                                 |                        | -80  |     | dB    |

| Off-Isolation                                   | V <sub>ISO</sub>     | $R_L = 50\Omega$ , $f = 20kHz$ , $V_{CD} = 0.5V_{P-P}$                                                                 |                        | -60  |     | dB    |

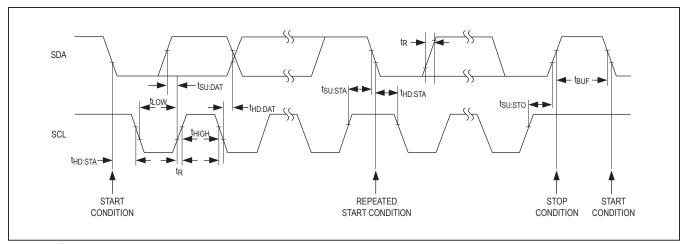

| I <sup>2</sup> C TIMING SPECIFICATIONS (        |                      |                                                                                                                        | •                      |      |     |       |

| I <sup>2</sup> C Maximum Clock                  | f <sub>I2C_CLK</sub> |                                                                                                                        |                        | 400  |     | kHz   |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>     |                                                                                                                        | 1.3                    |      |     | μs    |

| START Condition Setup Time                      |                      |                                                                                                                        | 0.6                    |      |     | μs    |

| Repeated START Condition<br>Setup Time          | t <sub>SU:STA</sub>  | 90% to 90%                                                                                                             | 0.6                    |      |     | μs    |

| START Condition Hold Time                       | t <sub>HD:STA</sub>  | 10% of SDA to 90% of SCL                                                                                               | 0.6                    |      |     | μs    |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub>  | 90% of SCL to 10% of SDA                                                                                               | 0.6                    |      |     | μs    |

| Clock Low Period                                | t <sub>LOW</sub>     | 10% to 10%                                                                                                             | 1.3                    |      |     | μs    |

| Clock High Period                               | tHIGH                | 90% to 90%                                                                                                             | 0.6                    |      |     | μs    |

| Data Valid to SCL Rise Time                     | t <sub>SU:DAT</sub>  | Write setup time                                                                                                       | 100                    |      |     | ns    |

| Data Hold Time to SCL Fall                      | t <sub>HD:DAT</sub>  | Write hold time                                                                                                        |                        |      | 0   | ns    |

$(V_{BAT}$  = +2.8V to +5.5V,  $V_{B}$  = +3.5V to +36V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{BAT}$  = +3.6V,  $V_{B}$  = +5.0V,  $T_{A}$  = +25°C.) (Note 4)

| PARAMETER      | SYMBOL | CONDITIONS       | MIN | TYP | MAX | UNITS |

|----------------|--------|------------------|-----|-----|-----|-------|

| ESD PROTECTION |        |                  |     |     |     |       |

| CD+, CD-, ID   |        | Human Body Model |     | ±15 |     | kV    |

| All Other Pins |        | Human Body Model |     | ±2  |     | kV    |

**Note 4:** All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design and not production tested.

Note 5: All resistor values guaranteed to be detected within ±1% range.

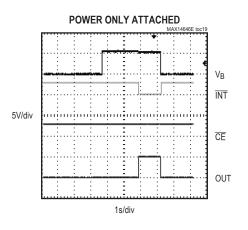

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Typical Operating Characteristics (continued)**

(TA = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

(T<sub>A</sub> = +25°C, unless otherwise noted.)

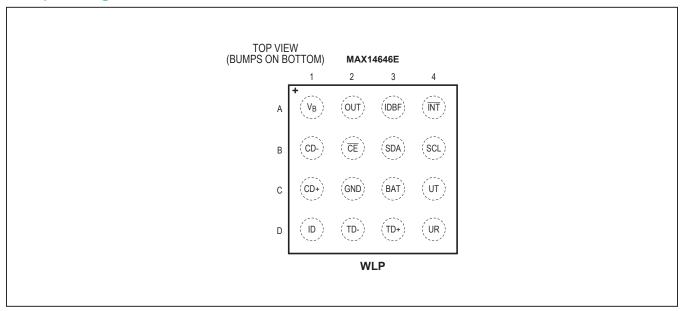

## **Bump Configuration**

## **Bump Description**

| BUMP | NAME           | FUNCTION                                                                                                       |

|------|----------------|----------------------------------------------------------------------------------------------------------------|

| A1   | V <sub>B</sub> | USB Connector V <sub>BUS</sub> Connection. Bypass V <sub>B</sub> with a 1µF capacitor to GND.                  |

| A2   | OUT            | Overvoltage-Protected USB Transceiver V <sub>BUS</sub> Power Output. Bypass OUT with a 1µF capacitor to GND.   |

| A3   | IDBF           | Push-Pull Digital ID Buffer Output                                                                             |

| A4   | ĪNT            | Active-Low, Open-Drain, Interrupt Request Fault Output. Connect INT to an external pullup resistor.            |

| B1   | CD-            | USB Connector D- Connection                                                                                    |

| B2   | CE             | Active-Low, Open-Drain, Charger Control Enable Output. Connect $\overline{CE}$ to an external pullup resistor. |

| В3   | SDA            | I <sup>2</sup> C Serial-Data Input/Output. Connect SDA to an external pullup resistor.                         |

| B4   | SCL            | I <sup>2</sup> C Serial-Clock Input. Connect SCL to an external pullup resistor.                               |

| C1   | CD+            | USB Connector D+ Connection                                                                                    |

| C2   | GND            | Ground                                                                                                         |

| C3   | BAT            | Battery Connection Input. Bypass BAT with a 1µF capacitor to GND.                                              |

| C4   | UT             | UART Tx Line from Device                                                                                       |

| D1   | ID             | USB Connector ID Connection. Bypass ID with a 1nF (max) capacitor to GND.                                      |

| D2   | TD-            | USB Transceiver D- Connection                                                                                  |

| D3   | TD+            | USB Transceiver D+ Connection                                                                                  |

| D4   | UR             | UART Rx Line from Device                                                                                       |

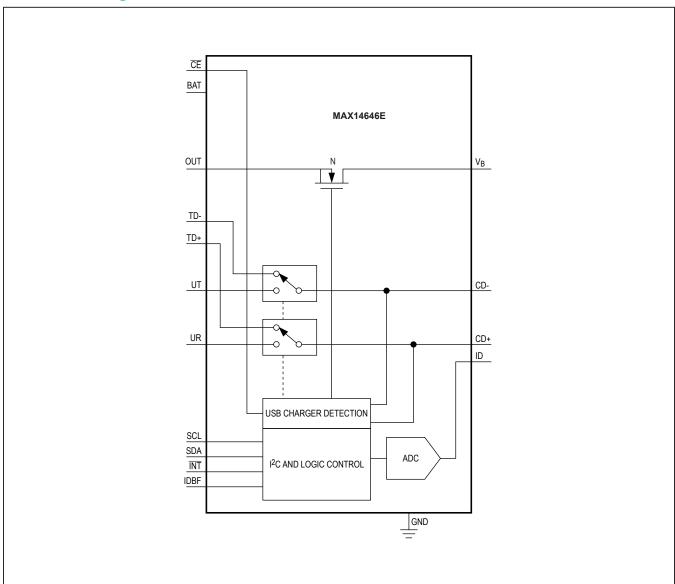

## **Functional Diagram**

## **Table 1. Register Map**

| ADDRESS | NAME        | B7          | В6                                       | B5                                   | B4  | В3        | B2      | B1          | В0         |

|---------|-------------|-------------|------------------------------------------|--------------------------------------|-----|-----------|---------|-------------|------------|

| 0x00    | DEVICE ID   |             | VENDO                                    | R_ID                                 |     |           | C       | CHIP_REV    |            |

| 0x01    | INTERRUPT 1 | DCD_TMR     | CHG_DET_START                            | CHG_DET_STOP                         | RF  | U         | OVP     | VB_VALID    | CHG_TYP    |

| 0x02    | INTERRUPT 2 | ADC_ERROR   |                                          | RFU                                  |     |           |         |             | ADC        |

| 0x03    | STATUS 1    | DCD_TMR_S   | CHG_DET_RUN_S OVP_S VB_VALID_S CHG_TYP_S |                                      |     |           |         |             |            |

| 0x04    | STATUS 2    | ADC_ERROR_S | RF                                       | U                                    |     |           | ADC_S   |             |            |

| 0x05    | INTMASK 1   | DCD_TMR_M   | CHG_DET_START_M                          | CHG_DET_STOP_M                       | RF  | U         | OVP_M   | VB_VALID_M  | CHG_TYP_M  |

| 0x06    | INTMASK 2   | ADC_ERROR_M |                                          |                                      | RFU |           |         |             | ADC_M      |

| 0x07    | CONTROL 1   | INT_TYP     | INT_DLY                                  | INT_DLY INT_POL INT_EN USB_SWC CP_EN |     | CP_EN     | LOW_PWR |             |            |

| 0x08    | CONTROL 2   | APPL_NXT    | CE_FRC                                   | CE_FRC CE ADC_DEB                    |     | DEB       | USB_CPL | ID_AUTO_SWC | ADC_EN     |

| 0x09    | CONTROL 3   | C           | DVP_EN                                   | /P EN CDP DET                        |     | DCD_2S_CT | DCD_EN  | CHG_TYP_MAN | CHG_DET_EN |

## **Table 2. Detailed Register Map**

| FIELD NAME         | READ/WRITE | BITS  | DEFAULT | DESCRIPTION                                                                                                                                           |

|--------------------|------------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVICE ID (0x00)   |            |       | ·       |                                                                                                                                                       |

| VENDOR_ID          | Read only  | [7:4] | 0010    | Vendor Identification                                                                                                                                 |

| CHIP_REV           | Read only  | [3:0] | 0000    | Chip Revision                                                                                                                                         |

| INTERRUPT 1 (0x01) |            |       |         |                                                                                                                                                       |

| DCD_TMR            | Read only  | [7]   | 0       | Data Contact Detection Timer Interrupt 0 = No interrupt 1 = Interrupt                                                                                 |

| CHG_DET_START      | Read only  | [6]   | 0       | Charger Detection Start Transition Interrupt 0 = No interrupt 1 = Interrupt                                                                           |

| CHG_DET_STOP       | Read only  | [5]   | 0       | Charger Detection Stop Transition Interrupt 0 = No interrupt 1 = Interrupt                                                                            |

| RFU                | Read only  | [4:3] | 00      | Reserved                                                                                                                                              |

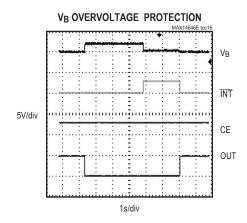

| OVP                | Read only  | [2]   | 0       | Overvoltage Protection Interrupt. When V <sub>B</sub> is greater than V <sub>OVP</sub> , the interrupt is triggered.  0 = No interrupt  1 = Interrupt |

| VB_VALID           | Read only  | [1]   | 0       | V <sub>BUS</sub> Valid Interrupt. Any change in the VB_VALID_S bit triggers an interrupt.  0 = No interrupt  1 = Interrupt                            |

| CHG_TYP            | Read only  | [0]   | 0       | Charger Type Interrupt 0 = No interrupt 1 = Interrupt                                                                                                 |

| INTERRUPT 2 (0x02) |            |       |         |                                                                                                                                                       |

| ADC_ERROR          | Read only  | [7]   | 0       | ADC Error Interrupt 0 = No interrupt 1 = Interrupt                                                                                                    |

**Table 2. Detailed Register Map (continued)**

| FIELD NAME       | READ/WRITE | BITS  | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

|------------------|------------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFU              | Read only  | [6:1] | 000000  | Reserved                                                                                                                                                                                                                                                                                                                                                      |

| ADC              | Read only  | [0]   | 0       | ADC Change Interrupt 0 = No interrupt 1 = Interrupt                                                                                                                                                                                                                                                                                                           |

| STATUS 1 (0x03)  |            | Г     | 1       |                                                                                                                                                                                                                                                                                                                                                               |

| DCD_TMR_S        | Read only  | [7]   | 0       | Data Contact Detection Timer Wait Status  0 = Data contact detection timer not expired or not running  1 = Data contact detection running for greater than 2s (typ)                                                                                                                                                                                           |

| CHG_DET_RUN_S    | Read only  | [6]   | 0       | Charger Detection State Machine Running Status 0 = Not running 1 = Running                                                                                                                                                                                                                                                                                    |

| OVP_S            | Read only  | [5]   | 0       | $V_B$ Overvoltage Protection Trip Level Indication $0 = V_B$ is less than or equal to the overvoltage trip level $1 = V_B$ is greater than the overvoltage trip level                                                                                                                                                                                         |

| VB_VALID_S       | Read only  | [4]   | 0       | $V_{BUS}$ Valid Status<br>$0 = V_B$ is less than $V_{VBDET}$ or $V_B$ is greater than the overvoltage trip level (OVP_S = 1)<br>$1 = V_B$ is greater than or equal to the $V_{VBDET}$ and $V_B$ is less than or equal to overvoltage trip level (OVP_S = 0)                                                                                                   |

| CHG_TYP_S        | Read only  | [3:0] | 0000    | USB Charger Detection Output 0000 = Nothing attached 0001 = Standard downstream port (SDP) 0010 = Charging downstream port (CDP) 0011 = Dedicated charger port (DCP) 0100 = Apple 500mA (max) charger 0101 = Apple 1A (max) charger 0110 = Apple 2A (max) charger 0111 = Special 500mA charger 1100 = Apple RFU Other conditions are reserved for future use. |

| STATUS 2 (0x04)  |            |       |         |                                                                                                                                                                                                                                                                                                                                                               |

| ADC_ERROR_S      | Read only  | [7]   | 0       | ADC Error Status 0 = No ADC error 1 = ADC error                                                                                                                                                                                                                                                                                                               |

| RFU              | Read only  | [6:5] | 00      | Reserved                                                                                                                                                                                                                                                                                                                                                      |

| ADC_S            | Read only  | [4:0] | 11111   | ADC Output. See the ADC Detection Resistors specifications in the <i>Electrical Characteristics</i> table.                                                                                                                                                                                                                                                    |

| INTMASK 1 (0x05) |            |       |         |                                                                                                                                                                                                                                                                                                                                                               |

| DCD_TMR_M        | Read/write | [7]   | 0       | Data Contact Detection Timer Interrupt Mask 0 = Mask 1 = Not masked                                                                                                                                                                                                                                                                                           |

| CHG_DET_START_M  | Read/write | [6]   | 0       | Charger Detection Run Rising Transition Interrupt Mask 0 = Mask 1 = Not masked                                                                                                                                                                                                                                                                                |

**Table 2. Detailed Register Map (continued)**

| FIELD NAME       | READ/WRITE | BITS  | DEFAULT | DESCRIPTION                                                                                                                                                                                                                            |

|------------------|------------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHG_DET_STOP_M   | Read/write | [5]   | 0       | Charger Detection Run Falling Transition Interrupt Mask 0 = Mask 1 = Not masked                                                                                                                                                        |

| RFU              | Read/write | [4:3] | 00      | Reserved                                                                                                                                                                                                                               |

| OVP_M            | Read/write | [2]   | 0       | Overvoltage Protection Interrupt Mask 0 = Mask 1 = Not masked                                                                                                                                                                          |

| VB_VALID_M       | Read/write | [1]   | 0       | V <sub>B</sub> Valid Interrupt Mask<br>0 = Mask<br>1 = Not masked                                                                                                                                                                      |

| CHG_TYP_M        | Read/write | [0]   | 0       | Charge Type Interrupt Mask 0 = Mask 1 = Not masked                                                                                                                                                                                     |

| INTMASK 2 (0x06) |            |       | •       |                                                                                                                                                                                                                                        |

| ADC_ERROR_M      | Read/write | [7]   | 0       | ADC Error Interrupt Mask 0 = Mask 1 = Not masked                                                                                                                                                                                       |

| RFU              | Read/write | [6:1] | 000000  | Reserved                                                                                                                                                                                                                               |

| ADC_M            | Read/write | [0]   | 0       | ADC Change Interrupt Mask 0 = Mask 1 = Not masked                                                                                                                                                                                      |

| CONTROL 1 (0x07) |            |       |         |                                                                                                                                                                                                                                        |

| INT_TYP          | Read/write | [7]   | 0       | This bit sets the interrupt type. See the <i>Interrupts</i> section for details.  0 = Interrupt is level triggered  1 = Interrupt is edge triggered                                                                                    |

| INT_DLY          | Read/write | [6]   | 0       | This bit sets the interrupt pulse width in case of trains of interrupt requests. This bit is valid only if INT_TYP = 1.  0 = 2 x 60kHz clock ticks  1 = 4 x 60kHz clock ticks                                                          |

| INT_POL          | Read/write | [5]   | 0       | This bit sets the interrupt polarity. See the <i>Interrupts</i> section for details.  0 = Active low 1 = Active high                                                                                                                   |

| INT_EN           | Read/write | [4]   | 0       | This bit enables interrupt generation. When INT_EN = 0, pending interrupts are not cleared and the INT pin acts as a FLAG per Table 4. INT_EN is a global setting to mask all interrupts.  0 = Disable interrupt  1 = Enable interrupt |

**Table 2. Detailed Register Map (continued)**

| FIELD NAME       | READ/WRITE | BITS  | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                               |

|------------------|------------|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_SWC          | Read/write | [3:2] | 11      | USB Switch Control 00 = All switches open 01 = USB switches connected to UT/UR position 10 = USB switches connected to TD+/TD- position 11 = Follow the detection finite state machine                                                                                                    |

| CP_EN            | Read/write | [1]   | 0       | Charge Pump Enable. To pass a negative signal to UR/UT, this bit must be set high.  0 = Charge pump disabled  1 = Charge pump enabled                                                                                                                                                     |

| LOW_PWR          | Read/write | [0]   | 1       | Low-Power Mode Enable 0 = Low-power mode disable. The oscillator and bandgap are always on. 1 = Low-power mode enable. The oscillator and bandgap are turned off when V <sub>BUS</sub> is not valid, USB_SWC = 00, CP_EN = 0, and ADC_S = 11111.                                          |

| CONTROL 2 (0x08) |            |       |         |                                                                                                                                                                                                                                                                                           |

| APPL_NXT         | Read/write | [7]   | 1       | Enable Next Possible Apple Charger (CHG_TYP = 1100) 0 = CHG_TYP = 1100 cannot be detected 1 = CHG_TYP = 1100 can be detected                                                                                                                                                              |

| CE_FRC           | Read/write | [6]   | 0       | Enable Force $\overline{\text{CE}}$ Outputs $0 = \overline{\text{CE}}$ output follow the charger detection finite state machine as per Table 3 $1 = \overline{\text{CE}}$ output forced as per CE bit configuration                                                                       |

| CE               | Read/write | [5]   | 0       | CE Output Forced Value. Valid only with CE_FRC = 1.  1 = CE output forced low  0 = CE output forced high impedance                                                                                                                                                                        |

| ADC_DEB          | Read/write | [4:3] | 01      | These bits set the ADC debounce time setting.  00 = 0.5ms (typ)  01 = 10ms (typ)  10 = 25ms (typ)  11 = 38.6ms (typ)                                                                                                                                                                      |

| USB_CPL          | Read/write | [2]   | 1       | USB Compliant Bit 0 = Device is not USB compliant 1 = Device is USB compliant                                                                                                                                                                                                             |

| ID_AUTO_SWC      | Read/write | [1]   | 1       | ID Auto Switch Control. ID resistor change during valid $V_B$ enables the auto switch configuration based on Table 3. $0$ = No auto switch configuration after the first auto configuration from initial valid $V_B$ 1 = Allow auto switch configuration based on ID while $V_B$ is valid |

**Table 2. Detailed Register Map (continued)**

| FIELD NAME       | READ/WRITE | BITS  | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC_EN           | Read/write | [0]   | 0       | ADC Enable. When ADC_EN is set low, the ADC is automatically enabled when valid $V_B$ is present and disabled when $V_B$ becomes invalid. When ADC_EN is set high, the ADC is always enabled regardless of $V_B$ . The device draws more quiescent current when ADC_EN is set high. $0 = \text{ADC disable with battery power only, and active only with valid } V_B$ $1 = \text{ADC always active}$ |

| CONTROL 3 (0x09) |            |       |         |                                                                                                                                                                                                                                                                                                                                                                                                      |

| OVP_EN           | Read/write | [7:6] | 10      | Manual Overvoltage Protection Control  00 = Force OVP open  01 = Force OVP closed V <sub>B</sub> > V <sub>VBDET</sub> 10 = OVP controlled by logic (closed after V <sub>BUS</sub> attach based on Table 4)  11 = Reserved for future use                                                                                                                                                             |

| CDP_DET          | Read/write | [5]   | 0       | USB Charger Downstream Detection Method 0 = Use V <sub>DP_SRC</sub> to drive D- 1 = Use weak pullup method                                                                                                                                                                                                                                                                                           |

| DCHK_TM          | Read/write | [4]   | 0       | Charger Type Detection Timer  0 = t <sub>DP_SRC_ON</sub> is set to 50ms  1 = t <sub>DP_SRC_ON</sub> is set to 620ms                                                                                                                                                                                                                                                                                  |

| DCD_2S_CT        | Read/write | [3]   | 1       | Data Contact Detection Exit Method 0 = Stay in DCD until normal exit 1 = Exit DCD when 2s (typ) interrupt asserts                                                                                                                                                                                                                                                                                    |

| DCD_EN           | Read/write | [2]   | 1       | Data Contact Detection State Machine Enable. If DCD is enabled, then before D+/D- is tested for a short, DCD must pass. If DCD is disabled, the DCD is skipped and D+/D-short detection begins. If DCD state machine is running for more than 2s (typ), the DCD timer interrupt is set high (DCD_TMR = 1).  0 = Disable 1 = Enable                                                                   |

| CHG_TYP_MAN      | Read/write | [1]   | 0       | Charger Type Manual Detection. This bit forces the internal logic to open the USB switches and perform charger type detection when set high. After the detection state machine completes, this bit self-resets.  0 = Disabled 1 = Enable charger detection                                                                                                                                           |

| CHG_DET_EN       | Read/write | [0]   | 1       | USB Charger Detection Enable 0 = Disable charger detection 1 = Enable charger detection                                                                                                                                                                                                                                                                                                              |

#### **Detailed Description**

The MAX14646E is a USB charger detector that includes features from USB Battery Charging Specification Revision 1.2. The IC features internal detection logic for determining the device connected and is controlled through the I<sup>2</sup>C interface. The device is a complete solution for multiplexing a USB and UART signal on a single USB connector with a Li+ battery charger.

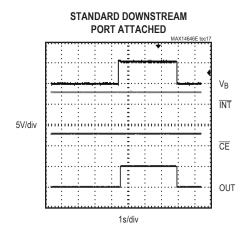

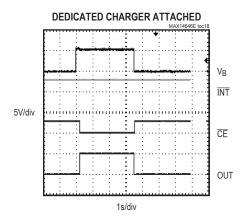

#### **USB Charger Detection**

The IC includes internal logic to detect if a valid USB charger is connected. When a valid  $V_{BUS}$  voltage is

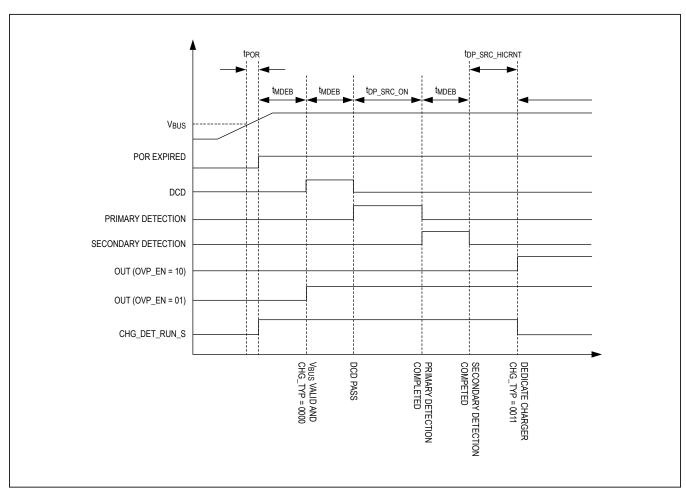

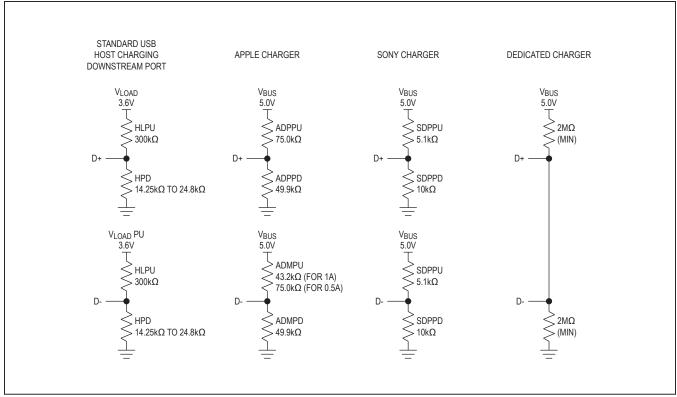

applied to V<sub>B</sub> or when CHG\_TYP\_MAN in the CONTROL 3 (0x09) register is set to 1, the device begins the charger type detection sequence. During the charger type detection sequence, the CD- and CD+ switches are open, and when the sequence completes, the switches return to their previous state. When the IC detects the charger, it sets the  $\overline{\text{CE}}$  output based on the charger found ( $\overline{\text{Table 3}}$ ). Figure 1 shows a timing diagram for an example charger type detection sequence. Figure 2 shows D+/D- termination for a standard USB host charging downstream port, Apple charger, Sony charger, and a dedicated charger.

Figure 1. Charger Detection Timing

Figure 2. Standard USB Host Charging Downstream Port, Apple Charger, Sony Charger, and Dedicated Charger

### **Table 3. Charger Control Output Status**

| CHG_TYP | CHARGER DETECTED         | CE OUTPUT   |             |  |

|---------|--------------------------|-------------|-------------|--|

| CHG_ITP | CHARGER DETECTED         | USB_CPL = 0 | USB_CPL = 1 |  |

| 0000    | Off                      | 1           | 1           |  |

| 0001    | Standard downstream port | 0           | 1           |  |

| 0010    | Charging downstream port | 0           | 0           |  |

| 0011    | Dedicated charger port   | 0           | 0           |  |

| 0100    | Apple 0.5A (max) charger | 0           | 0           |  |

| 0101    | Apple 1A (max) charger   | 0           | 0           |  |

| 0110    | Apple 2A (max) charger   | 0           | 0           |  |

| 0111    | Special 500mA charger    | 0           | 0           |  |

| 1100    | Reserved                 | 0           | 0           |  |

#### **Detection Debounce**

To avoid multiple interrupts at the insertion of an accessory and for added noise/disturbance protection, a debounce timer 30ms (typ) is present that requires an inserted or removed state hold for the debounce time before it sends an interrupt.

#### **USB Switch (CD+, CD-)**

The device supports Hi-Speed, full-speed, and low-speed USB signal levels. The USB channel is bidirectional and has low  $3\Omega$  (typ) on-resistance and 7pF (typ) on-capacitance. The low on-resistance is stable as the analog input signals are swept from ground to  $V_{SWPOS}$  for low signal distortion. This channel can pass negative audio signal without distortion when CP\_EN = 1.

#### **USB Switch (UT, UR)**

The IC supports standard single-supply UART signals. The UART channel supports high-speed signals. The UART channel is bidirectional and has low  $2.4\Omega$  (typ) onresistance. This channel can pass negative audio signal without distortion when CP EN = 1.

#### **Overvoltage Protection**

The IC features overvoltage protection up to +36V (max) on the  $V_{BUS}$  line. If the input voltage exceeds the overvoltage lockout cutoff threshold ( $V_{OVLO}$ ), the internal FET with low  $60m\Omega$  (typ) on-resistance disconnects the input from the output and protects low-voltage systems against voltage faults. The device features soft-start capability to minimize inrush current by slowly turning the internal FET on when the  $V_B$  voltage is valid for a period longer than the debounce time ( $t_{MDEB}$ ). When the overvoltage event occurs, the fault flag or interrupt is asserted depending on the INT\_EN configuration in the CONTROL 1 (0x07) register.

#### **Thermal Shutdown**

The IC features thermal shutdown protection to protect the device from fault conditions. When the die temperature is +150°C, the device enters thermal shutdown mode and the fault flag or interrupt is asserted depending on INT\_EN configuration in the CONTROL 1 (0x07) register. When the die temperature drops by 20°C, the device automatically resumes operation and the fault flag or interrupt is cleared.

#### Supply Voltage Selector

The supply voltage selector chooses between  $V_B$  and BAT inputs to power the internal blocks. If  $V_B$  is not present,  $V_{CCINT}$  is supplied from BAT. A typical 100 $\mu$ s POR is provided at the rising edge of  $V_{CCINT}$ .

#### Interrupts

The MAX14646E generates an interrupt for any change in VB\_VALID\_S, when DCD\_TMR\_S transitions from 0 to 1, and when an overvoltage and thermal shutdown events occur. The INT\_EN bit in the CONTROL 1 register (0x07) enables interrupt output. When INT\_EN sets to disable, all interrupts are masked, but not cleared. A read to the INTERRUPT 1 register (0x01) and INTERRUPT 2 register (0x02) is required to clear the interrupts. The INT pin is defaulted as a  $\overline{\text{FLAG}}$  function when the interrupt is disabled (INT\_EN = 0). The  $\overline{\text{INT}}$  pin is pulled low when an invalid or an unknown charger is inserted.

#### **Level-Triggered Interrupt**

Set the INT\_TYP bit in the CONTROL 1 (0x07) register low to select a level-triggered interrupt. Any unmasked interrupt event drives the INT line to its active level, and then holds it at that level until the interrupt register is read or cleared. Set the INT\_POL bit in the CONTROL 1 (0x07) register to configure the active level of the INT line. Since multiple events share a level-triggered interrupt line, upon detecting assertion of the interrupt line, the host must read the entire interrupt registers. After servicing the interrupt, the host rechecks the interrupt line status to determine if an interrupt is pending.

#### **Edge-Triggered Interrupt**

Set the INT\_TYP bit in the CONTROL 1 (0x07) register high to select an edge-triggered interrupt. Any unmasked interrupt event toggles the  $\overline{\text{INT}}$  line to its active level with a pulse width set by the INT\_DLY bit in the CONTROL 1 (0x07) register. Set the INT\_POL bit in the CONTROL 1 (0x07) register to configure the active level of the  $\overline{\text{INT}}$  line. If another interrupt occurs before the toggle is not over, the new interrupt event extends the toggle time by the period set by the INT\_DLY bit in the CONTROL 1 (0x07) register.

#### **Low-Power Modes**

The IC has CP\_EN and LOW\_PWR bits in the CONTROL 1 register (0x07) dedicated to low-power operation. CP\_EN controls the charge pump required for proper operation of the analog switches. When set to disable, no negative rail voltage can be applied.

The LOW\_PWR bit sets low-power mode. In low-power mode, the internal oscillator is turned off under the following conditions: no  $V_{BUS}$ , USB\_SWC = 00, CP\_EN = 0, and ADC\_S = 1111. When low-power mode is enabled, all switches are high impedance. Note that no negative rail voltage can be applied.

When low-power mode is disabled, the oscillator and bandgap are always on. If  $V_{BUS}$  is not present, the low-power mode can be disabled, the switches can be closed, and the battery power mode can be enabled using I<sup>2</sup>C commands.

#### **Digital Inputs**

The digital inputs must be designed to be compatible with 1.8V logic.

#### **Digital Outputs**

The digital outputs are open drain with the exception of IDBF. The IDBF pin has three possible states: GND, high impedance, and an output based on the ID resistor value. Table 4 shows the output status with different ID resistor settings.

#### **Micro-USB ID Input**

The resistor to GND at the ID pin of the USB connector determines the factory operating mode as defined in Table 3 and *Electrical Characteristics* table.

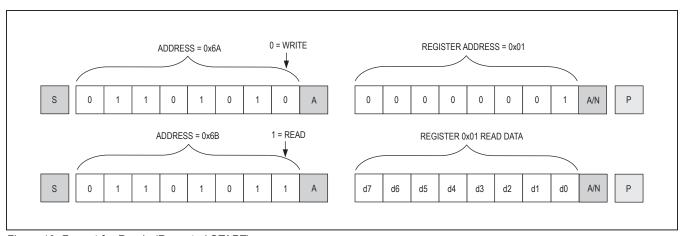

#### I<sup>2</sup>C Serial Interface

#### Serial Addressing

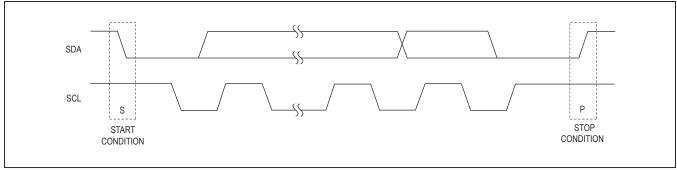

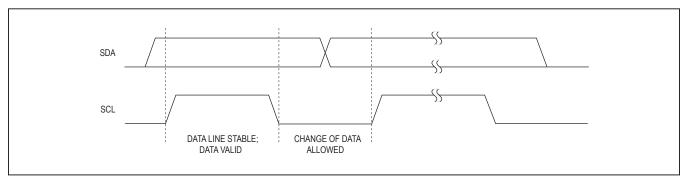

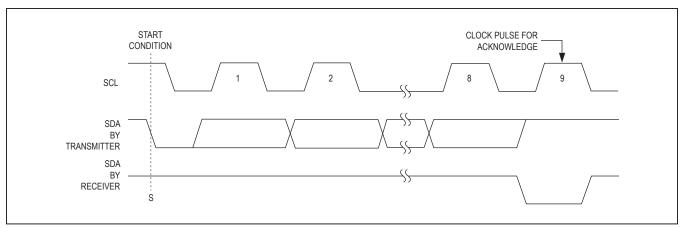

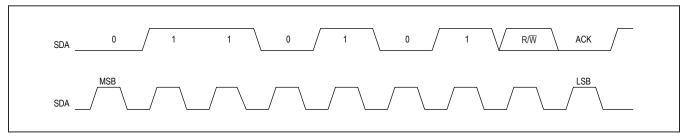

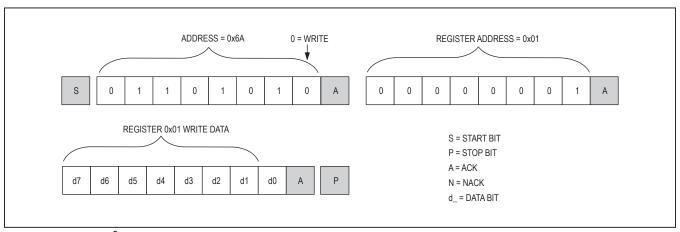

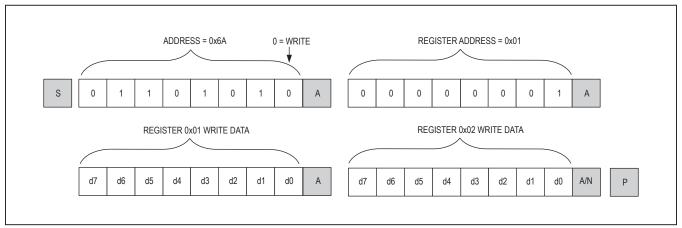

The IC operates as a slave device that sends and receives data through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial-data line (SDA) and a serialclock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the IC and generates the SCL clock that synchronizes the data transfer. The SDA line operates as both an input and an open-drain output. A pullup resistor is required on SDA. The SCL line operates only as an input. A pullup resistor is required on SCL if there are multiple masters on the 2-wire interface, or if the master in a single-master system has an open-drain SCL output. Each transmission consists of a START (S) condition (Figure 4) sent by a master, followed by the MAX14646E 7-bit slave address plus R/W bit, a register address byte, one or more data bytes, and finally a STOP (P) condition.

Table 4. Output Status\*

|                | STATUS |                  |                |           |                  |                  |                    |                |                |

|----------------|--------|------------------|----------------|-----------|------------------|------------------|--------------------|----------------|----------------|

| MAX14646E      | RESET  | INVALID          | отс            | UART      | USB/<br>FACTORY  | UART/<br>FACTORY | UNKNOWN<br>CHARGER | CHARGER        | USB<br>DEVICE  |

| V <sub>B</sub> | 0V     | Not<br>Connected | Connected      | Connected | Connected        | Connected        | Connected          | Connected      | Connected      |